# **CTU CAN FD**

## **IP CORE**

### **System Architecture**

LOGIC DESIGN SERVICES I.t.d.

February 1, 2026

| Document version | Corresponding Datasheet version (release) | Date       | Change description                                                                                                                              |

|------------------|-------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1              | 2.2                                       | 26-09-2019 | Initial version - separated stand-alone architecture document from Datasheet document.                                                          |

| 0.2              | 2.2                                       | 29-09-2019 | TX Arbitrator loads identifier as part of TXT buffer validation.                                                                                |

| 0.3              | 2.2                                       | 07-10-2019 | Update interfaces                                                                                                                               |

| 0.4              | 2.2                                       | 21-10-2019 | Clarify TXT buffer will go to TX Failed in Bus-off.                                                                                             |

| 0.5              | 2.2                                       | 07-11-2019 | Replace SSP shift register by SSP generator.                                                                                                    |

| 0.6              | 2.2                                       | 13-12-2019 | Add "Error delimiter too long" state to Protocol control FSM. Clear non-actual TODOs.                                                           |

| 0.7              | 2.2                                       | 30-04-2020 | Add note about implementation types. Remove form error on EDL/R0. Update Protocol control FSM to handle protocol exception.                     |

| 0.8              | 2.2.4                                     | 18-05-2020 | Correct Expected segment lenght preload values for negative resynchronisation.                                                                  |

| 0.9              | 2.2.5                                     | 6-10-2020  | Update Protocol control FSM diagram.                                                                                                            |

| 0.10             | 2.3.0                                     | 6-02-2021  | Add notes on clock gating.                                                                                                                      |

| 0.11             | 2.3.3                                     | 26-04-2021 | Add description of memory testability.                                                                                                          |

| 0.12             | 2.3.4                                     | 10-05-2021 | Keep NBTM counter enabled always even in data bit rate. Fixes bug with improper PH2 lenght if error is detected during data bit rate with BRP=1 |

| 0.13             | 2.3.5 and higher                          | 16-05-2021 | Add <b>res_n_out</b> synchronized reset output.                                                                                                 |

| 0.14             | 2.4 and higher                            | 22-12-2021 | Clarify implications of connecting core to 8/16/32 bit buses.                                                                                   |

| 0.15             | 2.4.1                                     | 10-4-2022  | Add Parity Check use-case in TXT buffer. Add <b>sup_parity</b> generic.                                                                         |

| 0.16             | 2.4.2                                     | 27-6-2022  | Add <b>reset_buffer_rams</b> and <b>active_timestamp_bits</b> generic. Remove interfaces of each sub-block.                                     |

| 0.17             | 2.4.3                                     | 18-2-2023  | Remove drv_bus and stat_bus.                                                                                                                    |

| 0.18             | 2.5                                       | 9-12-2023  | Move to new release of CTU CAN FD. Bump document version accordingly.                                                                           |

| 0.19             | 2.6                                       | 29-03-2025 | Replace GHDL with NVC                                                                                                                           |

| 0.20             | 2.6                                       | 15-6-2025  | Clean-up. Add missing RX buffer FSM states.                                                                                                     |

| 0.21             | 2.7                                       | 4-1-2026   | Move to new release of CTU CAN FD                                                                                                               |

# Contents

|                                               |           |

|-----------------------------------------------|-----------|

| <b>Format</b>                                 | <b>1</b>  |

| <b>1 General Information</b>                  | <b>2</b>  |

| 1.1 Introduction . . . . .                    | 2         |

| 1.2 Development tools . . . . .               | 2         |

| 1.3 Design automation . . . . .               | 2         |

| 1.3.1 Register map generation . . . . .       | 3         |

| 1.3.2 Xilinx Vivado component . . . . .       | 3         |

| 1.4 General coding guidelines . . . . .       | 3         |

| 1.5 Source code access . . . . .              | 4         |

| 1.6 ISO11898-1 2015 compliance . . . . .      | 4         |

| <b>2 Interfaces</b>                           | <b>7</b>  |

| 2.1 Memory Bus . . . . .                      | 7         |

| 2.1.1 RAM-like interface . . . . .            | 7         |

| 2.1.2 APB . . . . .                           | 8         |

| 2.1.3 AHB . . . . .                           | 10        |

| 2.1.4 Limitations on 8/16 bit buses . . . . . | 11        |

| 2.2 CAN Bus . . . . .                         | 11        |

| 2.3 Timestamp . . . . .                       | 12        |

| 2.4 Clock and reset . . . . .                 | 12        |

| 2.5 Test probe . . . . .                      | 12        |

| 2.6 Scan enable . . . . .                     | 12        |

| 2.7 Configuration options . . . . .           | 13        |

| <b>3 System architecture</b>                  | <b>14</b> |

| 3.1 Block diagram . . . . .                   | 14        |

| 3.2 Reset architecture . . . . .              | 14        |

| 3.3 Clock architecture . . . . .              | 15        |

| 3.4 Testability . . . . .                     | 16        |

| 3.4.1 Memory testability . . . . .            | 16        |

|                                                        |           |

|--------------------------------------------------------|-----------|

| 3.5 Sequential logic . . . . .                         | 16        |

| 3.6 Resynchronisers . . . . .                          | 17        |

| 3.7 Memories . . . . .                                 | 17        |

| 3.8 Pipeline architecture and triggers . . . . .       | 18        |

| 3.9 CAN Frame metadata . . . . .                       | 20        |

| 3.10 CAN Frame format . . . . .                        | 20        |

| 3.11 Test mode . . . . .                               | 21        |

| 3.12 Integration vs. Reintegration . . . . .           | 22        |

| <b>4 Sub-blocks architecture</b> . . . . .             | <b>23</b> |

| 4.1 CAN Core . . . . .                                 | 23        |

| 4.1.1 Protocol control . . . . .                       | 25        |

| Protocol control FSM . . . . .                         | 26        |

| Control counter . . . . .                              | 28        |

| Retransmitt counter . . . . .                          | 29        |

| Error detector . . . . .                               | 37        |

| 4.1.2 Operation control . . . . .                      | 40        |

| 4.1.3 Fault confinement . . . . .                      | 42        |

| 4.1.4 Bit stuffing . . . . .                           | 43        |

| 4.1.5 Bit destuffing . . . . .                         | 46        |

| 4.1.6 CAN CRC . . . . .                                | 47        |

| 4.1.7 Trigger multiplexor . . . . .                    | 50        |

| 4.1.8 Bus traffic counters . . . . .                   | 51        |

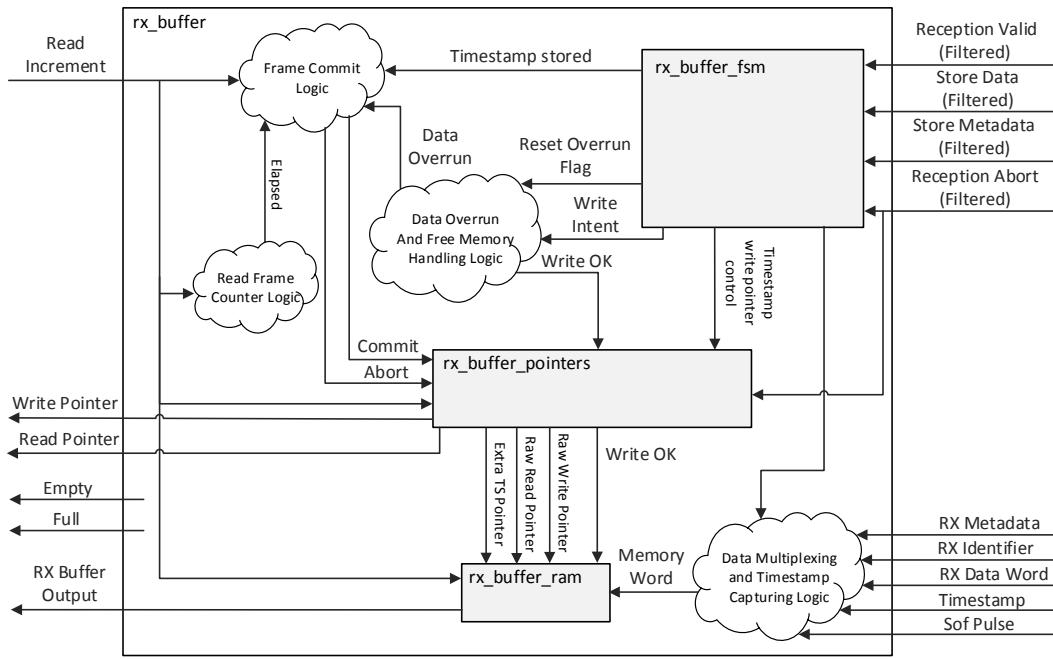

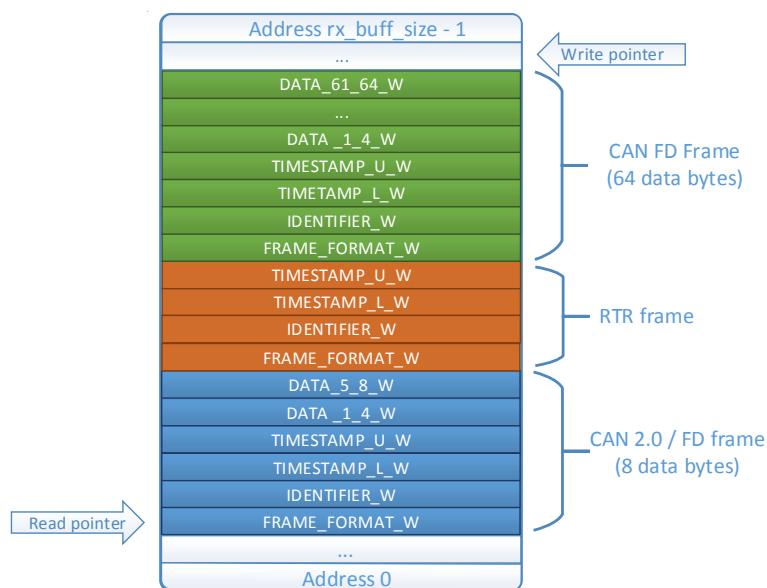

| 4.2 RX buffer . . . . .                                | 51        |

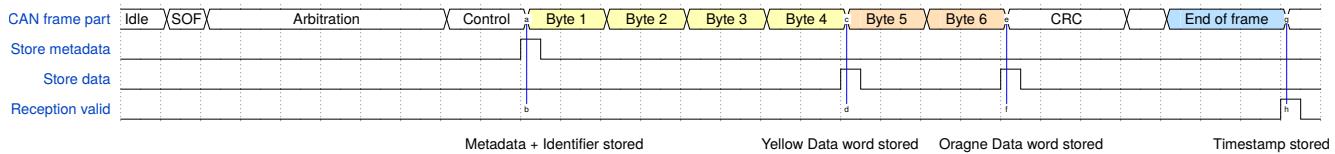

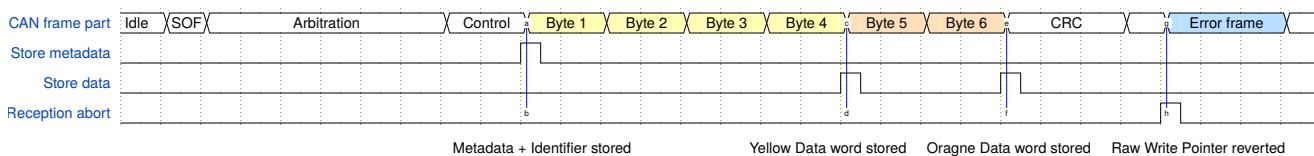

| 4.2.1 Storing protocol . . . . .                       | 53        |

| 4.2.2 Overrun flags . . . . .                          | 56        |

| 4.2.3 Received frame timestamp . . . . .               | 56        |

| 4.2.4 RX buffer Parity . . . . .                       | 56        |

| 4.2.5 Reading protocol . . . . .                       | 56        |

| 4.2.6 RX buffer RAM . . . . .                          | 58        |

| 4.3 Frame Filters . . . . .                            | 59        |

| 4.4 TXT buffer . . . . .                               | 60        |

| 4.4.1 TXT buffer commands . . . . .                    | 61        |

| 4.4.2 TXT buffer RAM . . . . .                         | 62        |

| 4.4.3 TXT buffer - Transmission availability . . . . . | 62        |

| 4.4.4 TXT buffer Parity . . . . .                      | 63        |

| 4.4.5 TXT buffer - Use cases . . . . .                 | 63        |

| 4.5 TX arbitrator . . . . .                            | 66        |

| 4.5.1 TXT buffer validation process . . . . .          | 67        |

---

|        |                                                   |    |

|--------|---------------------------------------------------|----|

| 4.5.2  | Priority decoder . . . . .                        | 71 |

| 4.5.3  | TXT buffer change between transmissions . . . . . | 73 |

| 4.5.4  | TX Arbitrator corner-cases . . . . .              | 73 |

| 4.5.5  | TXT buffer addressing . . . . .                   | 74 |

| 4.5.6  | TXT buffer RAM access . . . . .                   | 74 |

| 4.5.7  | TX frame timestamp comparison . . . . .           | 74 |

| 4.5.8  | Lock and Unlock commands . . . . .                | 75 |

| 4.5.9  | Metadata double-buffering . . . . .               | 75 |

| 4.5.10 | TX datapath hazard protection . . . . .           | 76 |

| 4.5.11 | TX Abort + Retransmitt clear . . . . .            | 76 |

| 4.6    | Interrupt Manager . . . . .                       | 77 |

| 4.7    | Prescaler . . . . .                               | 78 |

| 4.7.1  | Bit rate configuration . . . . .                  | 79 |

| 4.7.2  | Bit time counters . . . . .                       | 79 |

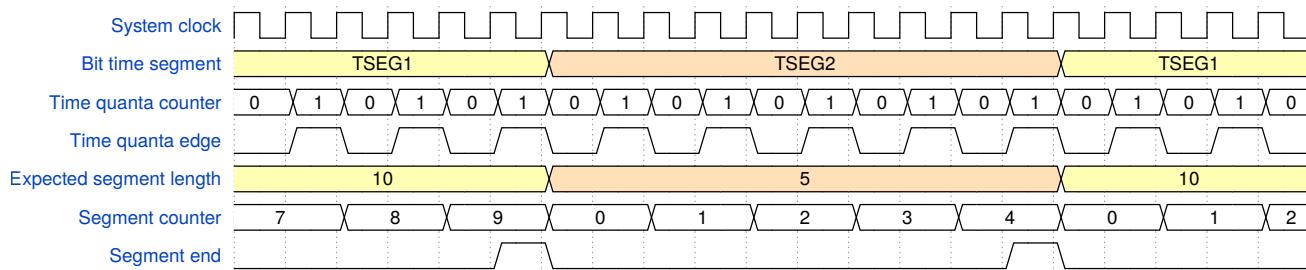

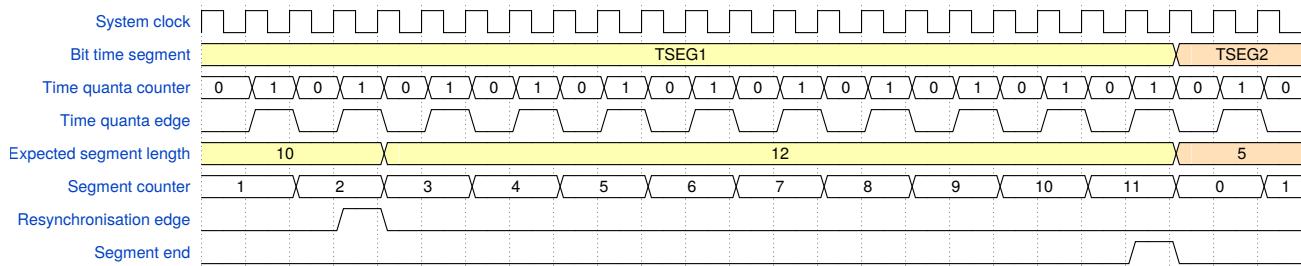

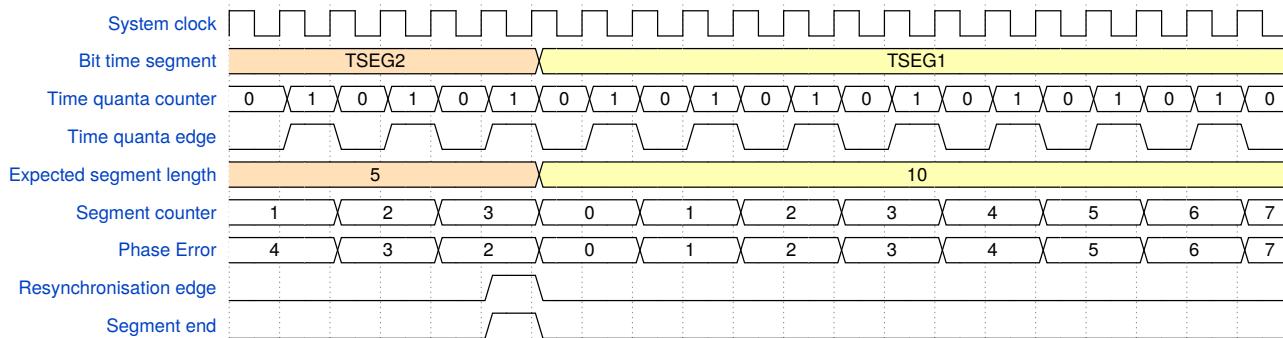

| 4.7.3  | Bit segment meter . . . . .                       | 79 |

| 4.7.4  | Segment end detector . . . . .                    | 81 |

| 4.7.5  | Bit rate switch . . . . .                         | 82 |

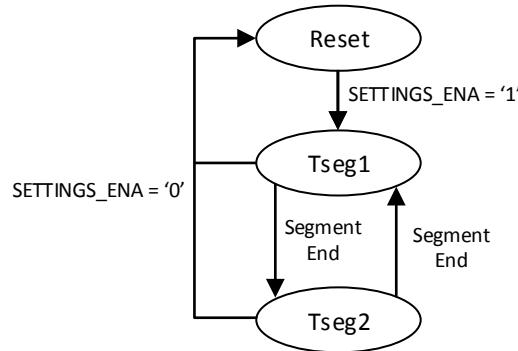

| 4.7.6  | Prescaler FSM . . . . .                           | 82 |

| 4.7.7  | Trigger generator . . . . .                       | 82 |

| 4.7.8  | Synchronisation control . . . . .                 | 84 |

| 4.7.9  | Synchronisation checker . . . . .                 | 84 |

| 4.8    | Bus sampling . . . . .                            | 86 |

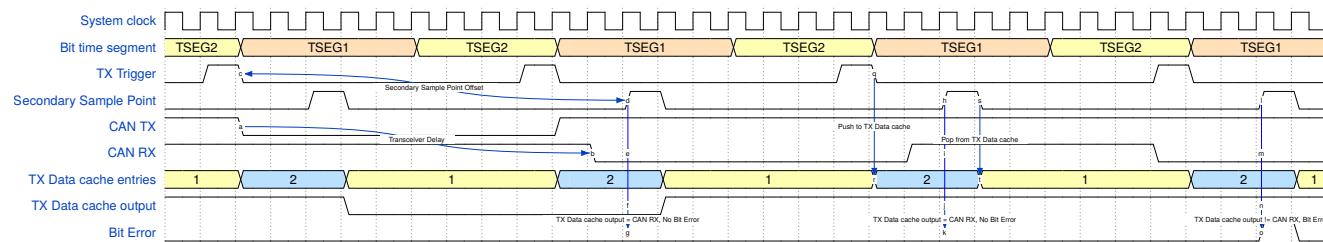

| 4.8.1  | Transmitter delay measurement . . . . .           | 87 |

| 4.8.2  | Secondary sampling point offset . . . . .         | 88 |

| 4.8.3  | Secondary sampling point generator . . . . .      | 88 |

| 4.8.4  | Bit error detection . . . . .                     | 89 |

| 4.8.5  | TX data cache . . . . .                           | 90 |

| 4.9    | Memory registers . . . . .                        | 91 |

| 4.9.1  | Register types . . . . .                          | 92 |

|        | Read/Write register . . . . .                     | 92 |

|        | Read only register . . . . .                      | 92 |

|        | Write only register . . . . .                     | 92 |

|        | Read/Write Once register . . . . .                | 92 |

| 4.9.2  | Register attributes . . . . .                     | 93 |

# Format

Throughout this document following notations are kept:

- Common text is written with this font.

- Memory registers are always described with capital letters e.g. REGISTER or REGISTER [BIT\_FIELD] to represent register or bit field within a register.

- Signal names and generic names are written by bold lower-case cursive (e.g. *can\_rx*)

- Explicit terms from ISO11898-1 2015 are marked via red color (e.g. **SOF** bit). Definition of these terms can be found in [1].

- Open issues and TODOs are written in blue font like so **TODO: not yet implemented**.

# 1. General Information

## 1.1 Introduction

This document describes architecture of CTU CAN FD IP Core. It describes external interfaces of the core as well as internal architecture. This document does not provide functional description of the core, reffer to CTU CAN FD Datasheet ([2]) for such information. This document align with CTU CAN FD Datasheet ([2]) serves as reference on how shall CTU CAN FD function, and it is supposed to be used as verification reference on how shall the device behave.

## 1.2 Development tools

To develop CTU CAN FD following tools are used:

- NVC for digital simulations.

- Quartus Prime and Xilinx Vivado for Synthesis to Intel and Xilinx FPGAs, Timing analysis and design size benchmarks.

- VUnit for simulation wrappers.

- Kactus2 for definition of register map in IP-XACT format.

- LyX to write documentation.

- GitLab of CTU FEE and Github to host source code GIT repository.

- Wavedrom for Timing Diagrams.

- Python for scripting.

## 1.3 Design automation

Part of CTU CAN FD Core is auto-generated. Register map is implemented in Kactus 2 in IP-XACT format ("spec/CTU/ip/CAN\_FD\_IP\_Core/2.1/CAN\_FD\_IP\_Core.2.1.xml"). The design in IP-XACT format is unified specification of user-interface. Following resources are generated from IP-XACT specification:

- VHDL packages with address, bit-fields and reset values definitions ("src/lib/can\_fd\_frame\_format.vhd", "src/lib/can\_fd\_register\_map.vhd").

- C header file with address map definitions and register descriptions (“driver/ctu\_can\_fd\_regs.h”, “driver/ctu\_can\_fd\_frame.h”).

- Lyx documentation of register map. Reffer to [2].

- RTL Code of Control Registers module (“src/memory\_registers/generated/\*”).

- Documentation of RTL module interfaces (“doc/core/entity\_docs”).

To generate these design materials CTU CAN FD IP Core uses IP-XACT register map generator which is accessible at regmap\_gen. Register map generator is linked as sub-module of CTU CAN FD repository. Clone all the submodules recursively before using register map generator. All of the generated files are considered as don't touch. Part of this document is also auto-generated. Each section which describes list of Generics and Signals of a module is generated from VHDL RTL code.

### 1.3.1 Register map generation

When CTU CAN FD GIT repository is clonned, register map can be generated by following script:

```

cd scripts

./update_reg_map

```

### 1.3.2 Xilinx Vivado component

CTU CAN FD contains Xilinx Vivado component (“src/component.xml”) for integration of CTU CAN FD to Xilinx based FPGAs. Xilinx Vivado component is generated by following script:

```

cd scripts

python gen_vivado_component.py

```

## 1.4 General coding guidlines

RTL code within CTU CAN FD has following coding rules:

- Underscore is always used to separate words within signal/entity/process/variable/port/generic names (e.g. tx\_hw\_cmd, can\_core).

- Constants are written by capital letters with “C\_” prefix (e.g. C\_SUSPEND\_DURATION).

- Generics are written by capital letters with “G\_” prefix (e.g. G\_RX\_BUFF\_SIZE). This rule has an exception on top level interface and wrappers of CTU CAN FD (can\_top\_level, can\_top\_ahb).

- Signals are always commented on line before the signal. This must be especially true for port signals. This allows to extract documentation of VHDL entities from RTL code.

- Sections of signals can be defined by surrounding section name by whole line of “-” characters.

- All RTL codes are indented with 4 spaces.

- Line length shall be limited to 80 characters.

- Instance names are suffixed with “\_inst”, process names are suffixed with “\_proc”, cover point names are suffixed with “\_cov”, assertion names are suffixed with “\_asrt”. DFF names can be suffixed by “\_d/\_q” depending on whether it is DFF input/output.

## 1.5 Source code access

CTU CAN FD IP Core source code is available in CTU FEE GitLab repository at:

[https://gitlab.fel.cvut.cz/canbus/ctucanfd\\_ip\\_core](https://gitlab.fel.cvut.cz/canbus/ctucanfd_ip_core)

## 1.6 ISO11898-1 2015 compliance

CTU CAN FD is compliant with [1]. With regards to this document, CTU CAN FD supports all implementation options (Classical CAN, CAN FD Tolerant, CAN FD enabled). Compliance to each of these options can be configured via a register (run-time configurable). Refer to [2] for description of CTU CAN FD configuration.

Support of optional features from [1] is described in Table 1.1 and Table 1.2.

Table 1.1: ISO11989-1 optional features (1)

| Feature Name                                      | Status              | Notes                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FD Frame format                                   | Supported           |                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Disabling of frame formats                        | Supported           | Reception of CAN FD frames can be disabled by setting MODE[FDE] = '0'.                                                                                                                                                                                                                                                                                                                                               |

| Limited LLC frames                                | Not Supported       | Only full size (64 byte) frames are supported.                                                                                                                                                                                                                                                                                                                                                                       |

| No transmission of frames including padding bytes | Not Supported       | No padding is inserted since full sized frames are supported.                                                                                                                                                                                                                                                                                                                                                        |

| LLC Abort Interface                               | Supported           | Issuing Set abort command to TXT buffer which is used for transmission is equal to issuing <a href="#">LDataAbort_Request</a> / <a href="#">LRemoteAbort_Request</a> primitive.                                                                                                                                                                                                                                      |

| ESI and BRS values                                | Supported           | BRS value can be specified for each transmitted CAN frame. ESI value can't be specified for transmitted CAN frames, it is always derived from current Fault confinement state of CTU CAN FD. ESI value can be read for each received frame.                                                                                                                                                                          |

| Method to provide MAC data consistency            | Partially Supported | CTU CAN FD implements TXT buffer RAMs which stores whole CAN frame for transmission before the transmission is started. This corresponds to: "The MAC sub-layer shall store the whole message to be transmitted in a temporary buffer that is filled before the transmission is started." Additionally, CTU CAN FD implements parity protection on each word of TXT buffer and RX buffer if <b>sup_parity</b> =true. |

| Time and time triggering                          | Partially Supported | Time triggered transmission is available in TX Arbitrator module. CTU CAN FD does not support time base by itself, it is left up to integrator to provide Time base via <b>timestamp</b> input. The reason for this, is to share single Time base between multiple instances of CTU CAN FD. <b>timestamp</b> input is readable from CTU CAN FD. No event generation is provided from <b>timestamp</b> input.         |

| Time stamping                                     | Supported           | Timestamping of RX frames is supported in SOF or EOF bit. Time Base counter must be provided by integrator and must be connected to <b>timestamp</b> input.                                                                                                                                                                                                                                                          |

| Bus Monitoring mode                               | Supported           | Supported via MODE[LOM].                                                                                                                                                                                                                                                                                                                                                                                             |

| Handle                                            | Supported           | Handle corresponds to TXT buffer.                                                                                                                                                                                                                                                                                                                                                                                    |

| Restricted operation                              | Supported           | Supported via MODE[ROM].                                                                                                                                                                                                                                                                                                                                                                                             |

| Separate prescalers for Nominal and Data Bit Rate | Supported           | Prescalers are separate in BTR[BRP] and BTR_FD[BRP_FD] registers.                                                                                                                                                                                                                                                                                                                                                    |

Table 1.2: ISO11989-1 optional features (1)

| Feature Name                                                        | Status        | Notes                                                                                                                           |

|---------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------|

| Disabling of automatic retransmission                               | Supported     | Supported via SETTINGS[RTRLE] and SETTINGS[RTRTH] registers.                                                                    |

| Maximum number of retransmissions                                   | Supported     |                                                                                                                                 |

| Disabling of protocol exception event on res bit detected recessive | Supported     | Protocol exception is configurable via SETTINGS[PEX] register.                                                                  |

| PCS_Status                                                          | Supported     | CTU CAN FD supports both <b>nominal</b> and <b>data</b> bit rate.                                                               |

| Edge filtering during the bus integration state                     | Not Supported |                                                                                                                                 |

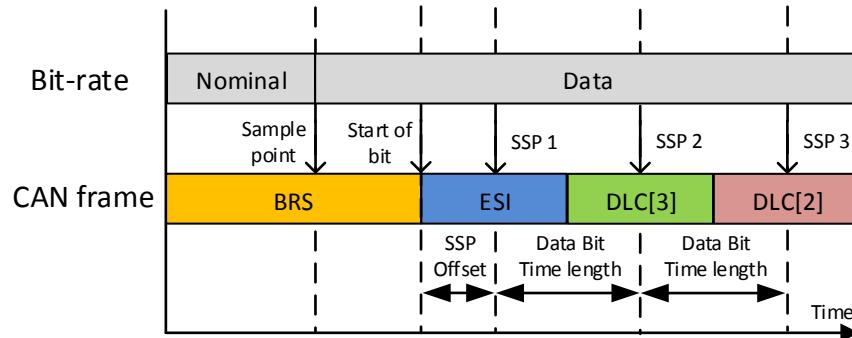

| Time resolution for SSP placement                                   | Not Supported | <b>Secondary sample point</b> position is always given in <b>minimum time quanta</b> regardless of bit rate prescaler settings. |

| FD_T/R message                                                      | Supported     |                                                                                                                                 |

## 2. Interfaces

### 2.1 Memory Bus

CTU CAN FD is a slave device accessible via one of three memory buses:

- RAM-like interface

- APB

- AHB

Each interface can be used via dedicated wrapper. SW shall not access CTU CAN FD sooner than two clock cycles after external reset was released (due to reset synchronisation) (see Table 3.1). If CTU CAN FD is accessed earlier, writes accesses have no effect and read accesses return zeroes. If external reset is executed via SW driver (e.g. at driver load time), it is recommended to add corresponding delay before driver executes any access to the device (e.g. via usleep, nanosleep, dummy NOPs, or similar mechanism).

#### 2.1.1 RAM-like interface

**Wrapper** can\_top\_level.vhd

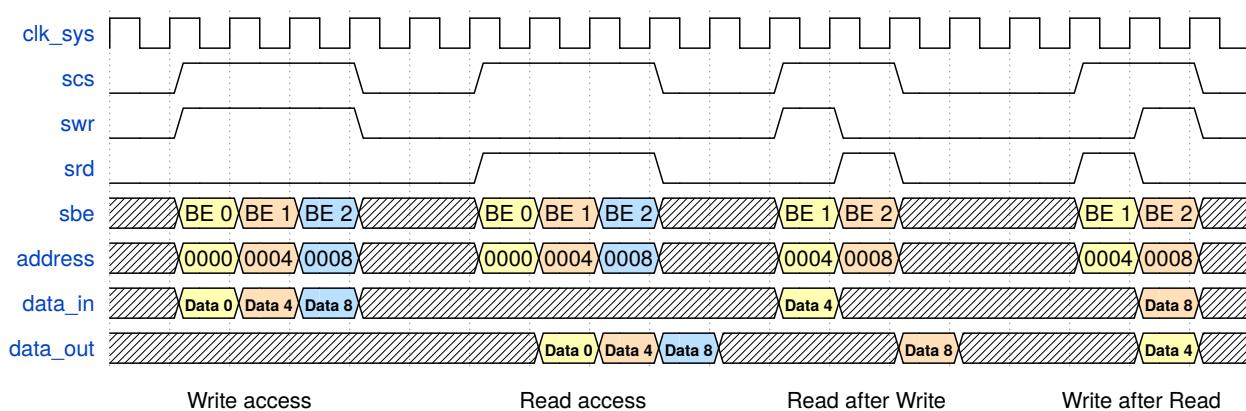

RAM-like interface is the default interface of CTU CAN FD with signals shown in Table 2.1. A typical read/write transactions on RAM-like interface are shown in Figure 2.1. Note that RAM-like interface does not contain any Ready/ACK signal. CTU CAN FD is always able to process written data in one clock cycle (write access) and return read data in the next clock cycle (read access). Accesses on RAM-like interface shall be 4 byte aligned (lower 2 bits of address shall be equal to 0). If access is not 4 byte aligned, lower 2 bits of address are ignored. Therefore, single access spanning more than 1 32 bit memory word is not possible. Each byte is separately writable and readable via byte enable (**sbe**), therefore 8-bit and 16-bit accesses are supported. If **sbe** signal is zero, data on corresponding byte are not written during write access, and zeroes are returned during read access. CTU CAN FD is little endian oriented (LSB = Lowest Adress -> **sbe(0)** = Byte 0 = **data\_in/out(7:0)**; **sbe(3)** = Byte 3 = **data\_in/out(31:24)**).

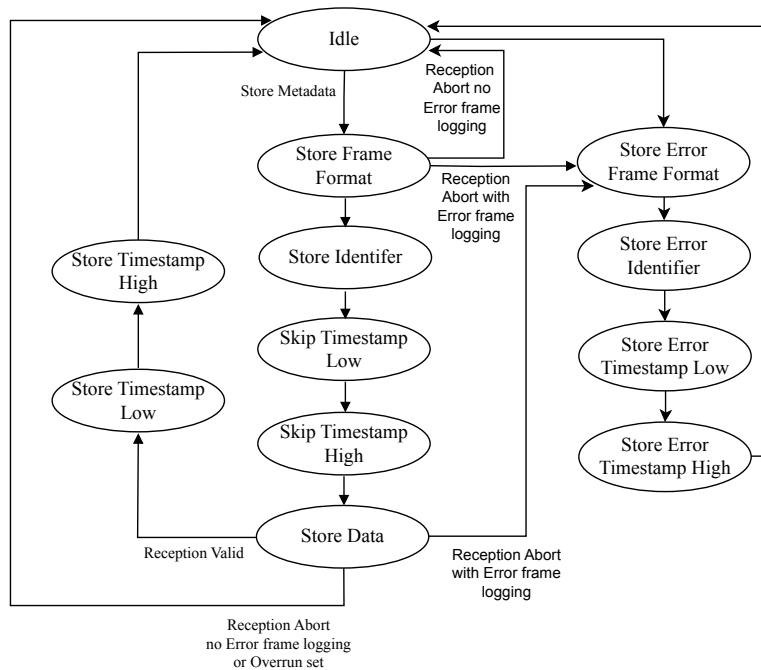

RAM-like interface supports burst read from RX buffer (see 4.2). In such case, **address** input must be equal to RX\_DATA register address during whole read operation ("stationary"/"frozen" burst). During such read, each word must be read by 32-bit access (**sbe**="1111"). This means that read from RX buffer is always executed by 32-bit word regardless of **sbe** value. Such a situation is shown in Figure 2.2.

Table 2.1: RAM-like interface

| Signal Name     | Direction | Width | Description                                        |

|-----------------|-----------|-------|----------------------------------------------------|

| <b>data_in</b>  | in        | 32    | Write Data                                         |

| <b>address</b>  | in        | 16    | Address                                            |

| <b>scs</b>      | in        | 1     | Chip Select                                        |

| <b>srd</b>      | in        | 1     | Read indication                                    |

| <b>swr</b>      | in        | 1     | Write indication                                   |

| <b>sbe</b>      | in        | 4     | Byte enable (applicable for both reads and writes) |

| <b>data_out</b> | out       | 32    | Read data                                          |

Figure 2.1: RAM-like interface

Figure 2.2: RX buffer burst read

RAM-like interface is Avalon compatible (according to [3]) and mapping of RAM like signals to Avalon Memory-mapped slave signals is shown in Table 2.2. When connected to Avalon MM master, write access to reserved address has no effect and read access returns all zeroes instead of responding with DECODEERROR response. **response** signal shall be connected to "00", **writeresponsevalid** and **readdatavalid** shall be connected to '1'.

### 2.1.2 APB

**Wrapper** can\_top\_apb.vhd

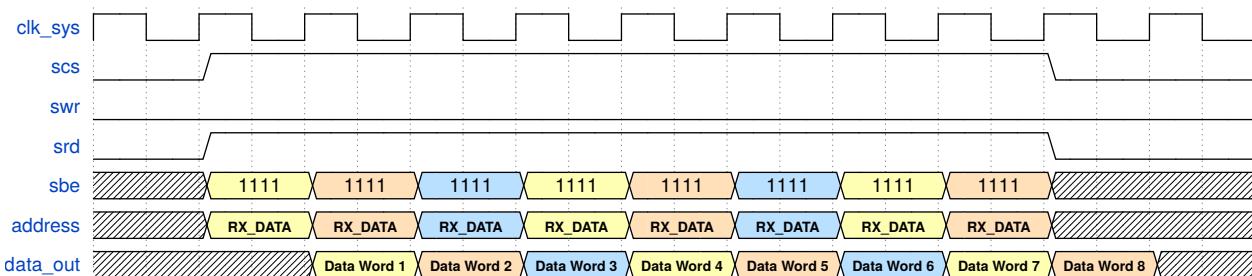

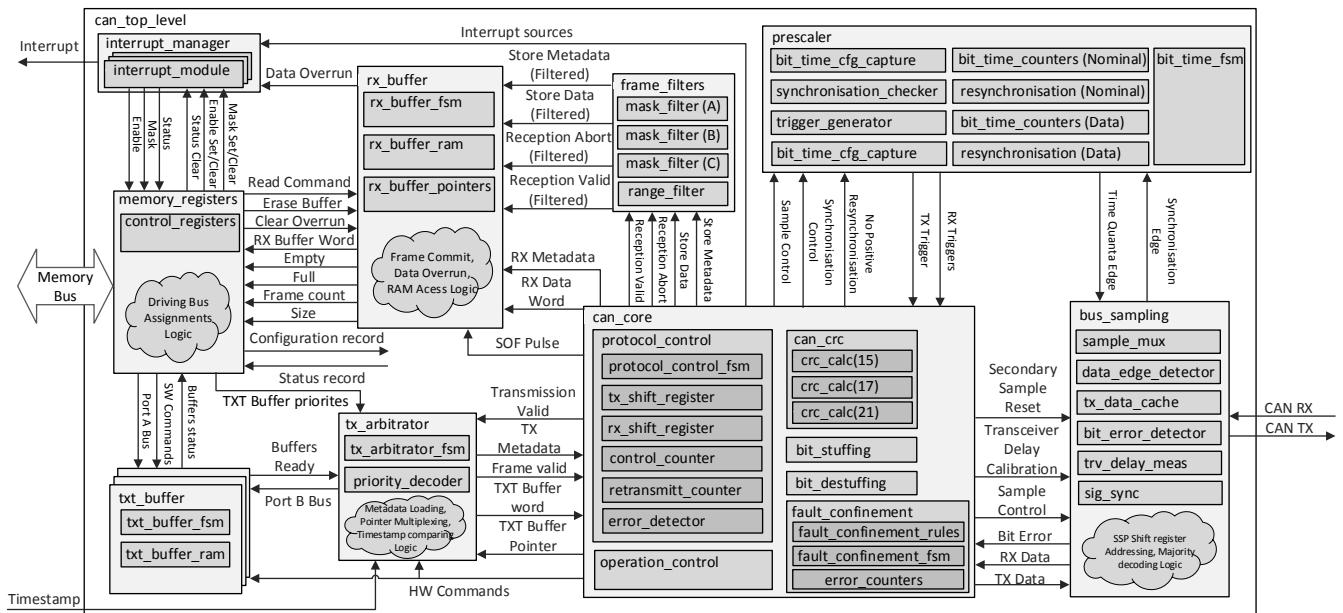

APB Wrapper is compatible with [4]. Signals of CTU CAN FD on APB interface are shown in Table 2.3. Every access on APB Interface lasts two clock cycles, APB does not support bursts. CTU CAN FD never stalls on APB interface via

Table 2.2: RAM-like to Avalon mapping

| RAM-like signal name | Avalon signal name | Description                                                                                                                                     |

|----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>data_in</b>       | <b>write_data</b>  | Data written to Avalon MM slave.                                                                                                                |

| <b>address</b>       | <b>address</b>     | Address for read/write of Avalon MM slave.                                                                                                      |

| <b>scs</b>           | -                  | Shall correspond to chip select of slave if more than 1 slave is connected to given bus. If single slave is connected, shall be connected to 1. |

| <b>srd</b>           | <b>read</b>        | Read indication                                                                                                                                 |

| <b>swr</b>           | <b>write</b>       | Write indication                                                                                                                                |

| <b>sbe</b>           | <b>byteenable</b>  | Byte enable, used for both read and write transfers.                                                                                            |

| <b>data_out</b>      | <b>readdata</b>    | Data read from Avalon MM slave.                                                                                                                 |

**s\_apb\_pready**, it keeps **s\_apb\_pready** always high. CTU CAN FD does not return error via **s\_apb\_pslverr** on any access. If SW executes access to an invalid location within CTU CAN FD, it is simply ignored. This allows dumping whole CTU CAN FD memory space without memory access errors. Accesses on APB Interface shall be 4 byte aligned. If access is not 4 byte aligned, lowest 2 bits of address are ignored. 8/16 bit write accesses are supported via write strobe signal (**s\_apb\_pstrb**). Basic accesses on APB are shown in Figure 2.3.

Table 2.3: APB interface

| Signal Name          | Direction | Width | Description                                                                                                      |

|----------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------|

| <b>s_apb_paddr</b>   | in        | 32    | Address                                                                                                          |

| <b>s_apb_penable</b> | in        | 1     | Enable. Indicates second cycle of access.                                                                        |

| <b>s_apb_prot</b>    | in        | 3     | Protection type. Ignored by CTU CAN FD. All access types are treated equally by CTU CAN FD.                      |

| <b>s_apb_prdata</b>  | out       | 32    | Read data.                                                                                                       |

| <b>s_apb_pready</b>  | out       | 1     | Ready. Always asserted.                                                                                          |

| <b>s_apb_psel</b>    | in        | 1     | Slave select.                                                                                                    |

| <b>s_apb_pslverr</b> | out       | 1     | Access error. CTU CAN FD always drives this pin low.                                                             |

| <b>s_apb_pstrb</b>   | in        | 4     | Write Strobe. During write access, logic 1 indicates according byte will be written. Ignored during read access. |

| <b>s_apb_pwdata</b>  | in        | 32    | Write data.                                                                                                      |

| <b>s_apb_pwrite</b>  | in        | 1     | Access direction.                                                                                                |

Figure 2.3: APB Interface access

### 2.1.3 AHB

**Wrapper** CAN\_top\_ahb.vhd

AHB Wrapper is compatible with [8]. Signals of CTU CAN FD on AHB interface are shown in Table 2.4. CTU CAN FD accepts all transfer types (Non-sequential, Sequential, Idle, Busy) on AHB bus. CTU CAN FD treats burst accesses equally as regular accesses (no internal caching is done). If read transfer occurs after write transfer (directly one after another), CTU CAN FD inserts one wait cycle into AHB transaction, as is shown in Figure 2.4. CTU CAN FD does not return error via **hresp** on any accesses. If SW executes access to an invalid location within CTU CAN FD, it is simply ignored. This allows dumping whole CTU CAN FD memory space without memory access errors. CTU CAN FD does not support unaligned accesses on AHB Bus. Each access shall be aligned to its own size (8-bit access can have arbitrary address, 16 bit access must have address 2-byte aligned, 32-bit access must have address 4-byte aligned). No locked sequences (**hmastlock**) are supported by CTU CAN FD.

Table 2.4: AHB interface

| Signal Name      | Direction | Width | Description                                            |

|------------------|-----------|-------|--------------------------------------------------------|

| <b>haddr</b>     | in        | 32    | Address                                                |

| <b>hwdata</b>    | in        | 32    | Write Data                                             |

| <b>hsel</b>      | in        | 1     | Write select                                           |

| <b>hwrite</b>    | in        | 1     | Access direction                                       |

| <b>hsize</b>     | in        | 3     | Access size. (8/16/32 bit access sizes are supported). |

| <b>hburst</b>    | in        | 3     | Burst indication, ignored by CTU CAN FD.               |

| <b>hprot</b>     | in        | 3     | Protection type, ignored by CTU CAN FD.                |

| <b>htrans</b>    | in        | 2     | Transaction type.                                      |

| <b>hmastlock</b> | in        | 1     | Locked sequence indication.                            |

| <b>hready</b>    | in        | 1     | Ready indication.                                      |

| <b>hreadyout</b> | out       | 1     | Ready indication output.                               |

| <b>hresp</b>     | out       | 1     | Response type.                                         |

| <b>hrdata</b>    | out       | 32    | Read data.                                             |

Figure 2.4: AHB Interface access

#### 2.1.4 Limitations on 8/16 bit buses

CTU CAN FD is 32-bit peripheral, however, it is possible to integrate it to systems with 8/16 bit bus thanks to “byte enable” capabilities of each bus interface wrapper. If SW accesses CTU CAN FD via 8/16 bit bus, access to simple 32-bit R/W register can be split into 4/2 consecutive accesses without affecting the functionality. However, due to side-effects on several registers, there are following limitations when accessing CTU CAN FD from 8/16 bit buses:

- CTU CAN FD must be used in RX buffer manual mode (MODE[RXBAM] = 0). This is necessary since read of single word from RX buffer can not be done by single read access to RX\_DATA register. On 8 bit systems, it will require 4 reads (addresses RX\_DATA .. RX\_DATA + 0x3), on 16 bit systems it will require 2 reads (addresses RX\_DATA and RX\_DATA + 0x2). Since each read from RX\_DATA register in RX buffer automated mode (MODE[RXBAM] = 1), will move RX buffer read pointer, the rest of the memory word would be lost without being read out. Thus it would be impossible to correctly read out received frames. Reading out RX buffer on 8/16 bit systems thus requires operation in MODE[RXBAM] = 0 and manually moving RX buffer read pointer by COMMAND[RXRPMV] bit.

- On 8 bit systems, TX\_PRIORITY register is only able to change priority of TXT buffers atomically if number of TXT buffers is 2. On 16 bit systems, TX\_PRIORITY register is only able to change priority of TXT buffers atomically, if number of TXT buffers is 2-4. Atomic change of TXT buffer priorities is required if TXT buffers are used like a FIFOs by priority rotation (such approach is used by CTU CAN FD Linux driver). Thus, if TXT buffer priorities need to be rotated atomically, following restrictions apply:

- On 8 bit systems, only 2 TXT buffers must be used.

- On 16 bit systems, only up to 4 TXT buffers must be used.

- If atomic rotation of priorities is not required, number of TXT buffers is not restricted.

## 2.2 CAN Bus

CTU CAN FD interfaces to physical layer transceiver via **can\_rx** and **can\_tx** pins. **can\_rx** input is assumed to be asynchronous to System clock (see 2.4) and it is treated like asynchronous signal. **can\_tx** output is synchronous to System clock. **can\_tx** output is glitch-free during operation on CAN bus as long as MODE[LOM] bit is not changed.

## 2.3 Timestamp

CTU CAN FD interfaces to system level Time base via **timestamp** input. **timestamp** input is assumed to be synchronous to System clock, and therefore there is no resynchronization on this input. If **timestamp** is unused (no Timestamping / Time Triggering capability), it shall be driven to 0xFFFF FFFF FFFF FFFF. If **timestamp** is used, it shall be driven by unsigned up-counting counter which measures flow of time within a system to which CTU CAN FD is being integrated. **timestamp** does not need to be incremented every clock cycle of System clock, nor there is a constraint on step that it is incremented with, it only needs to be synchronous to System clock. If system level time counter has lower width than 64 bits, integrating system shall connect such counter to lower bits of **timestamp** input, and drive unused high bits to zero. Integrating system shall also set **active\_timestamp\_bits** to width of such counter - 1 (e.g. when system has 32 bit timestamp, it shall be connected to **timestamp[31:0]** and **active\_timestamp\_bits**=31).

## 2.4 Clock and reset

CTU CAN FD is clocked via single clock input which represents System clock domain. Name of clock signal is different depending on used memory bus wrapper as is shown in Table 2.5. CTU CAN FD has single external reset which is treated as asynchronous reset, and it is internally synchronized by reset synchronizer (see 3.3). Note that AHB bus specifications requires **hresetn** to be synchronous to **hclk**. CTU CAN FD implementation is more relaxed, and does not require these signals to be synchronous to **hclk** (System clock), since it handles reset synchronisation internally. **res\_n\_out** signal output contains synchronized version of **res\_n/arstn/hresetn** input. It can be left unconnected, or it can be used as an indication that reset has been completed and CTU CAN FD can be accessed on its memory bus.

Table 2.5: Clock signal names

| Bus type | Clock signal name | Reset signal name |

|----------|-------------------|-------------------|

| RAM-like | <b>sys_clk</b>    | <b>res_n</b>      |

| APB      | <b>aclk</b>       | <b>arstn</b>      |

| AHB      | <b>hclk</b>       | <b>hresetn</b>    |

## 2.5 Test probe

CTU CAN FD contains **test\_probe** record output. This signal is used by CTU CAN FD test-bench to peek inside the design of CTU CAN FD. When integrating CTU CAN FD, this output can remain un-connected. Reffer to [8] for description of how to connect test-probe if integrating CTU CAN FD VIP. This signal has no effect on design functionality, and it can remain unconnected in design to which CTU CAN FD is integrated.

## 2.6 Scan enable

CTU CAN FD design is DFT insertion friendly. When **scan\_enable** = 1, CTU CAN FD is in scan mode. In scan mode, the following is valid:

- All hand-instantiated clock gates in CTU CAN FD are un-gated (to make sure that scan chain is always clocked).

- All resets which depend on value of other flip-flops are gated (to avoid resetting part of scan chain during scan operation).

**scan\_enable** input shall be controlled by SoC level DFT controller, and it shall be connected to the same signal which enables scan mode on inserted scan flip-flops. If CTU CAN FD is used in FPGA (**target\_technology** = 1), **scan\_enable** shall be tied low. **scan\_enable** signal shall be driven synchronous to System clock.

## 2.7 Configuration options

CTU CAN FD is configurable on top level interface via VHDL generics which are explained in Table 2.6.

Table 2.6: CTU CAN FD generic parameters

| Name                         | Type    | Default | Range      | Description                                                          |

|------------------------------|---------|---------|------------|----------------------------------------------------------------------|

| <b>rx_buf_size</b>           | natural | 128     | 32-4096    | Size of RX buffer RAM in 32 bit words. See 4.2.                      |

| <b>txt_buffer_count</b>      | natural | 4       | 2-8        | Number of TXT buffers. See 4.4.                                      |

| <b>sup_filt_A</b>            | boolean | true    | true/false | Synthesize filter A. See 4.3.                                        |

| <b>sup_filt_B</b>            | boolean | true    | true/false | Synthesize filter B. See 4.3.                                        |

| <b>sup_filt_C</b>            | boolean | true    | true/false | Synthesize filter C. See 4.3.                                        |

| <b>sup_range</b>             | boolean | true    | true/false | Synthesize range filter. See 4.3.                                    |

| <b>sup_traffic_counters</b>  | boolean | true    | true/false | Synthesize traffic counters. See 4.1.8.                              |

| <b>target_technology</b>     | natural | 1       | 0-1        | Target technology (set 0 for ASIC, set 1 for FPGA).                  |

| <b>sup_test_registers</b>    | boolean | true    | true/false | Synthesize test registers.                                           |

| <b>sup_parity</b>            | boolean | false   | true/false | Add parity protection to TXT buffers / RX buffer.                    |

| <b>reset_buffer_rams</b>     | boolean | false   | true/false | When true, TXT buffer and RX buffer RAMs are reset by <b>res_n</b> . |

| <b>active_timestamp_bits</b> | integer | 63      | 0-63       | Number of active timestamp bits minus - 1.                           |

# 3. System architecture

## 3.1 Block diagram

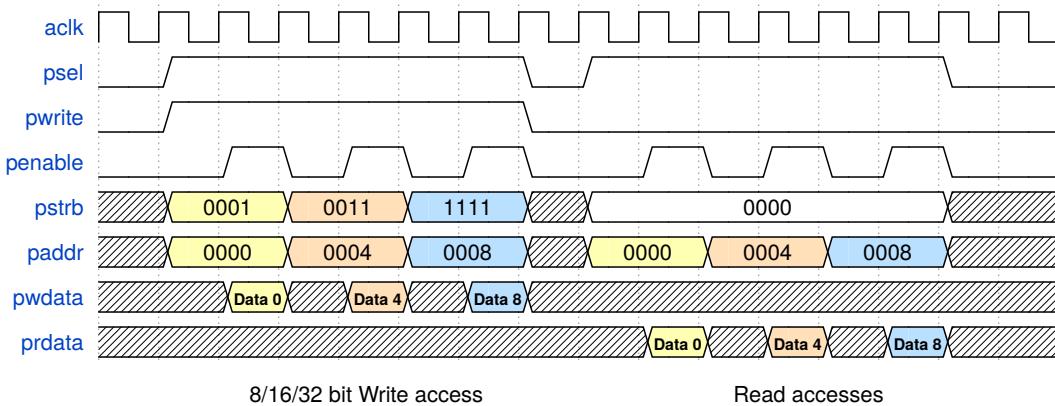

Detailed block diagram of CTU CAN FD IP Core is shown in Figure 3.1.

Figure 3.1: CTU CAN FD - Detailed block diagram

## 3.2 Reset architecture

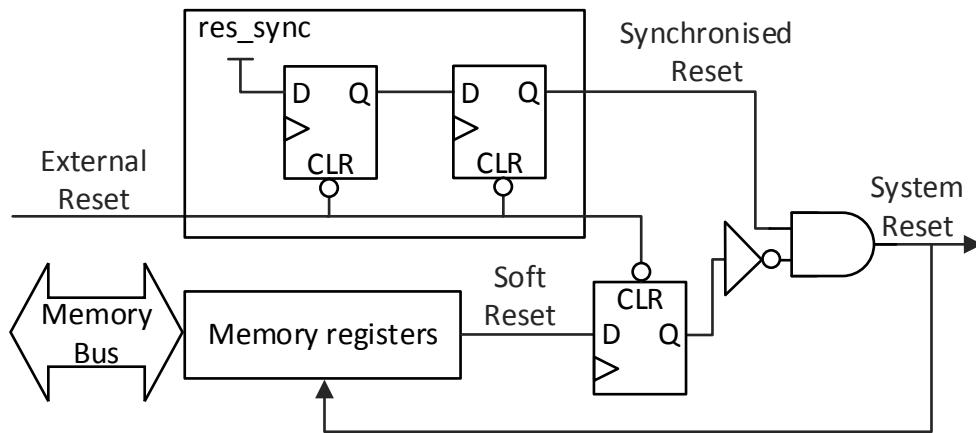

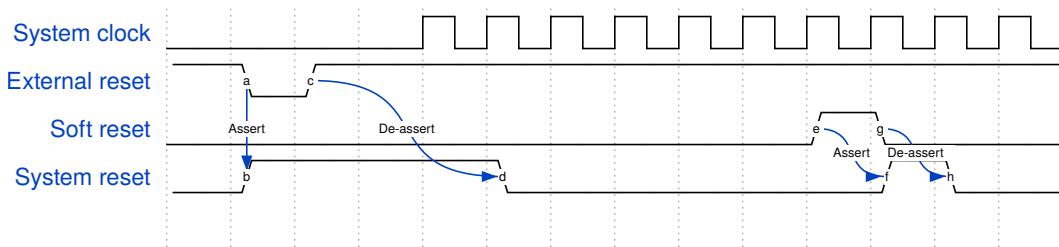

CTU CAN FD IP Core can be reset by two means: External reset and Soft Reset. Both reset sources are described in Table 3.1. Both reset cause assertion of internal System reset which resets whole CTU CAN FD including Memory registers. Reset architecture is shown in Figure 3.2. An example of reset sequence by both External and Soft reset are shown in Figure 3.3. Note that all DFFs in Figure 3.2 are clocked by System clock.

Table 3.1: Reset description

| Reset Name     | Asserted by                               | Reset description                                                                                                                                                                                                                                                                                                                                                     |

|----------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External Reset | RAM like interface:<br><b>res_n = 0</b> . | To be used by HW reset structure integrating CTU CAN FD (e.g. POR, System level reset controller). CTU CAN FD shall not be accessed for two System clock periods after External reset was de-asserted (or until <b>res_n_out = 1</b> ). Asserting External reset does not require System clock to be running. De-asserting reset requires System clock to be running. |

|                | AHB interface:<br><b>hresetn = 0</b> .    |                                                                                                                                                                                                                                                                                                                                                                       |

|                | APB interface:<br><b>aresetn = 0</b> .    |                                                                                                                                                                                                                                                                                                                                                                       |

| Soft Reset     | Writing MODE[RST] = '1'.                  | To be used by SW for resetting CTU CAN FD. System clock must be running when this reset is asserted (needed for Bus access and pipeline DFF).                                                                                                                                                                                                                         |

Figure 3.2: Reset structure

Figure 3.3: Reset operation

### 3.3 Clock architecture

CTU CAN FD IP Core contains one clock domain: System clock. There are no divided clocks in CTU CAN FD, thus no “generated clocks” are needed when writing SDC constraints. All timing related information (e.g. **time quanta**) are derived from System clock via clock enable signals. This makes CTU CAN FD fully synchronous design with no clock domain crossing.

CTU CAN FD is assumed to be implemented in a single power domain, all parts of CTU CAN FD must be either turned on or off. To reduce dynamic power consumption, majority of registers are written to allow usage of “clock enables” (FPGAs) or inferred “clock gating” (ASIC).

If **target\_technology** = 0 (ASIC), hand-written clock gating is implemented for Memory registers, RX buffer RAM and TXT buffer RAMs. If **target\_technology** = 1 (FPGA), no hand-written clock gating is implemented, clocks for memory registers RX buffer RAMs, and TXT buffer RAMs are always enabled. There is no functional difference between ASIC/FPGA target technology (even if clocks are always enabled, registers are written only when enabled).

The manually used clock gating cell (clk\_gate.vhd) has Latch + AND type. It is recommended to replace clk\_gate with Integrated clock gating cell by rewriting content of clk\_gate.vhd.

If **target\_technology** = 1 (FPGA), then clk\_gate.vhd does not gate clocks, but only connects input clock to output clock.

If CTU CAN FD is implemented in SoC system, it is recommended to implement configurable clock gating for whole CTU CAN FD peripheral on system level to save power when CTU CAN FD is not clocked. In such situation, CTU CAN FD ignores traffic on CAN Bus, and continuously transmits **recessive** bits to CAN Bus.

## 3.4 Testability

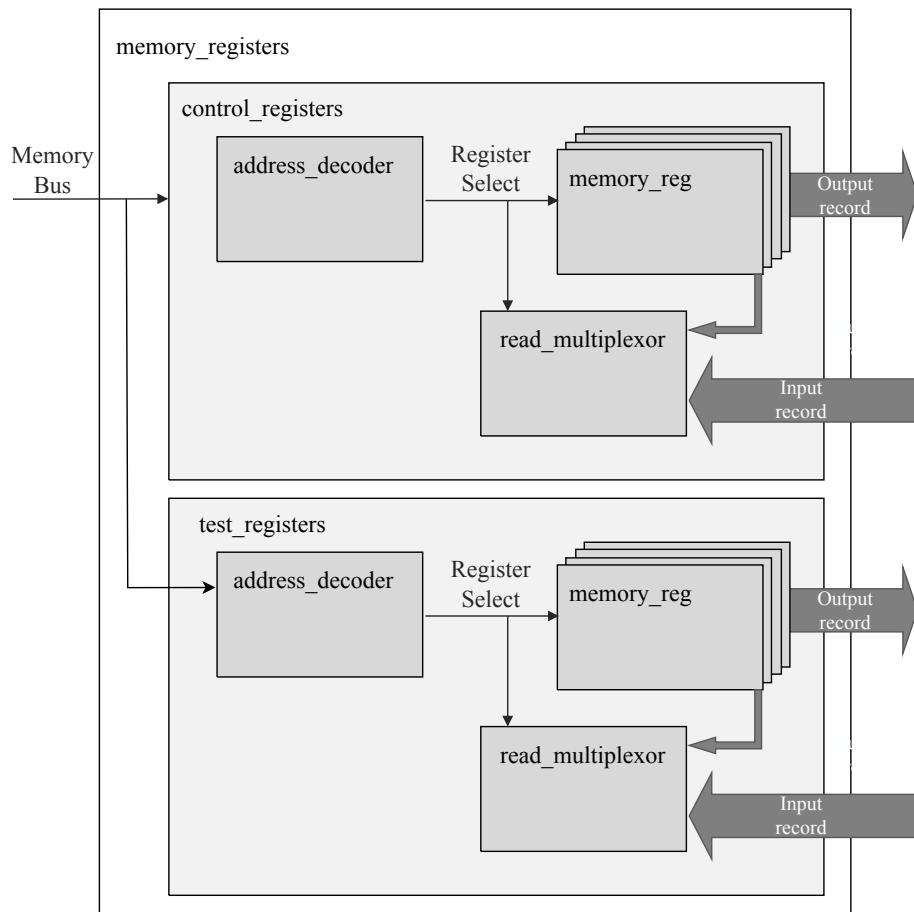

CTU CAN FD contains following features for manufacturing testability:

1. Memory testability - Allows direct read/write access to TXT buffer RAMs and RX buffer RAM. This approach is supported only when Test registers memory region is synthesized (**sup\_test\_registers** = true). It is recommended to synthesize Test registers only for ASIC implementations (**target\_technology** = 0). Enabling Test registers for FPGA implementations is useful only to test parity protection of RX / TXT buffer RAMs, since access from Test Registers bypasses parity encoding mechanism.

2. Scan mode (via **scan\_enable** input) - In scan mode, all clock gates are enabled, and all reset signals which depend on other signals (generated reset) are gated.

### 3.4.1 Memory testability

Each memory within CTU CAN FD can be tested at production via Test Registers (e.g. executing SW driven march pattern test). Any data can be written to any address inside each memory. Memory testability is available only in Test Mode (MODE[TSTM] = 1). If CTU CAN FD is not in Test mode, accesses to whole Test registers block are ignored. Memory testability has its own “enable” bit (TSTCTRL[TMENA]), which must be set to enable memory testing via Test Registers. An example of memory testing is shown in Table 3.2. Note that this test sequence is only an example. Since Test registers provide independent Read/Write functionality to arbitrary addresses, any known testing approach can be used (any address step, direction or data pattern can be used).

## 3.5 Sequential logic

CTU CAN FD logic is implemented from DFFs with asynchronous reset.

TXT buffer and RX buffer RAMs (see 3.7) are by default implemented from DFFs. All DFFs are active on positive clock edge. CTU CAN FD is latch free (apart from latches within clock gate cells). These facts can be used as a sanity check that there should be no DFFs without Set and Reset within CTU CAN FD after synthesis (apart from TXT buffer / RX buffer RAMs, if they are synthesized, not inferred, nor replaced by Hard RAM macros).

Table 3.2: Memory testing example

| Step | Action                                                                                                                                                               |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Set MODE[TSTM] = 1 and TSTCTRL[TMENA] = 1. This enables memory testing.                                                                                              |

| 2    | Configure target memory to be tested in TST_DEST[TST_MTGT] register. Set TST_DEST[TST_ADDR] = 0 (initial address).                                                   |

| 3    | Write test pattern to TST_WDATA register. It is up to user to choose test pattern.                                                                                   |

| 4    | Execute write to the memory by writing TSTCTRL[TWRSTB] = 1. Note that TSTCTRL[TMAENA] must remain set.                                                               |

| 5    | Increment address in TST_DEST[TST_ADDR]. If this is last address within tested memory, then go to Step 6. Otherwise go to Step 3.                                    |

| 6    | Set TST_DEST[TST_ADDR] = 0 (initial address).                                                                                                                        |

| 7    | Wait for 1 System clock clock cycle (read from RAMs is pipelined).                                                                                                   |

| 8    | Read value from TST_RDATA. Check that value read from this register matches what has been written TST_WDATA register in Step 3. If value does not match, test fails. |

| 9    | Increment address in TST_DEST[TST_ADDR]. If this is last address within tested memory, then go to Step 10. Otherwise go to Step 7.                                   |

| 10   | Test is successfull.                                                                                                                                                 |

## 3.6 Resynchronisers

Resynchronisers within CTU CAN FD IP Core are listed in Table 3.3.

Table 3.3: Resynchronisers

| Resynchroniser function                 | Resynchroniser Type | Resynchroniser path                                  |

|-----------------------------------------|---------------------|------------------------------------------------------|

| Resynchronisation of External Reset     | Reset Synchroniser  | can_top_level\rst_sync_inst                          |

| Resynchronisation of CAN RX Data Stream | Signal Synchroniser | can_top_level\bus_sampling_inst\can_rx_sig_sync_inst |

## 3.7 Memories

CTU CAN FD contains memories which are used to store CAN FD frames. These memories are parts of RX buffer and TXT buffers (see 4.2 and 4.4). List of memories is shown in Table 3.4. The TXT buffers and RX buffers can be either with or without reset:

- If **reset\_buffer\_rams** = false, TXT buffer RAMs and RX buffer RAM are not reset.

- The memories initialize to X.

- On FPGA, SRAM / BRAM blocks are inferred.

- On ASIC, DFT insertion may be complicated since DFFs of TXT buffer and RX buffer RAM are not controllable.

- ASIC fault-coverage can be achieved by functional test via Test Registers.

- If **reset\_buffer\_rams** = true, TXT buffer RAMs and RX buffer RAM are reset.

- The memories initialize to 0.

- On FPGA, SRAM / BRAM blocks will not be inferred.

- On ASIC, DFT insertion is easy since DFFs of TXT buffer and RX buffer are as any other registers.

- ASIC fault coverage can be achieved by DFT + ATPG, no need to synthesize Test Registers.

When integrating CTU CAN FD to ASIC, integrator can either replace these memories by hard macros, or leave memory implementation to synthesis tool. In such case, memory is synthesized from DFFs.

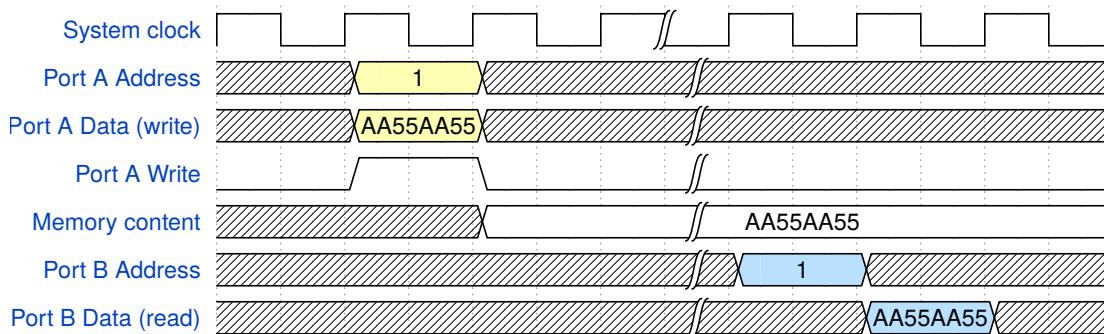

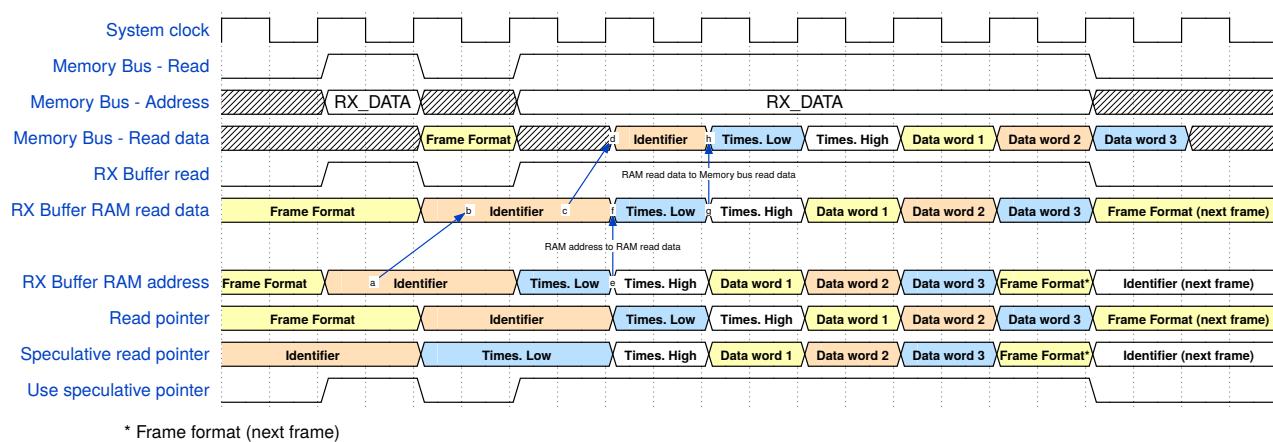

Each memory is synchronous memory with one clock cycle latency on data read, and one cycle write access latency. Both memories are dual port memories with write-only port A, read-only port B, and the same clock signal is used to clock both ports. If true dual port memories are used, write data/enable of Port B shall be driven to 0. Memory word width is 32 bits, and it must support byte-enable capability. An example of memory access is shown in Figure 3.4. In case of read during write, memories return old data value, there is no “bypassing” implemented.

Table 3.4: RAM memories

| Memory location | Write mask | Instance Name  | Instances | Depth   | Word Width | Address size | Port A Access    | Port B Access    | Read        |

|-----------------|------------|----------------|-----------|---------|------------|--------------|------------------|------------------|-------------|

| RX buffer RAM   | No         | rx_buffer_ram  | 1         | 32-4096 | 32         | 5-12         | CAN Core         | Memory Registers | Synchronous |

| TXT buffer RAM  | No         | txt_buffer_ram | 2-8       | 20      | 32         | 5            | Memory registers | CAN Core         | Synchronous |

Figure 3.4: Dual port memories access

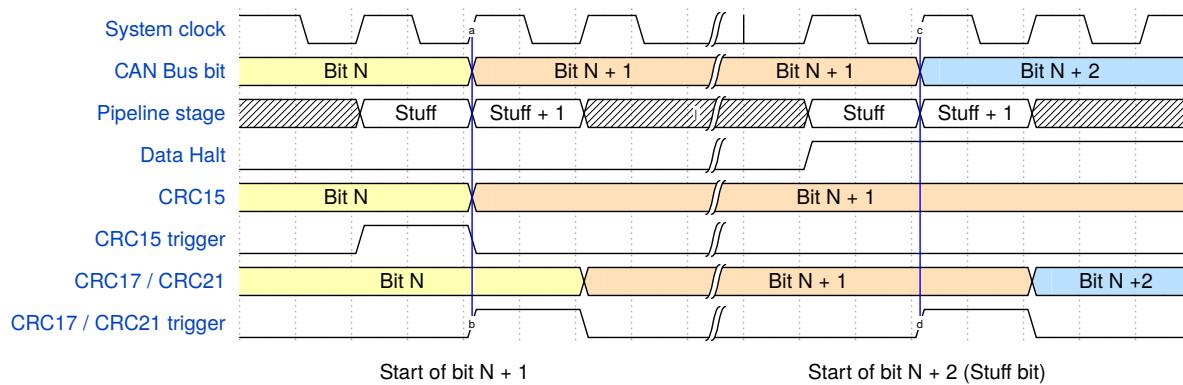

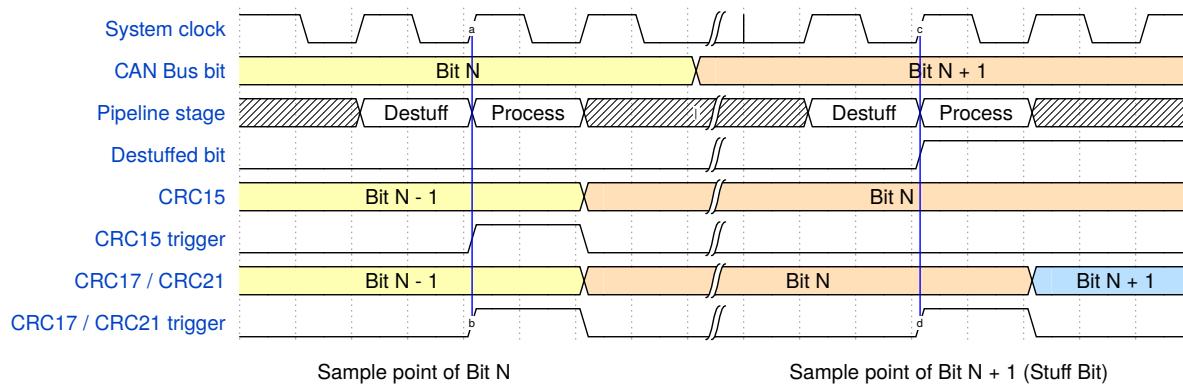

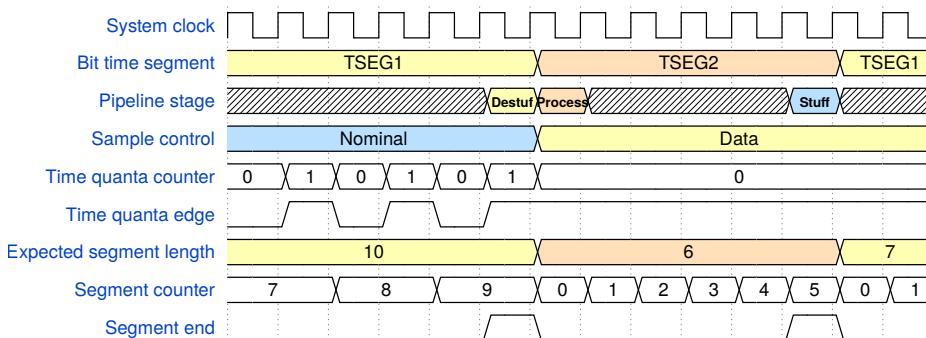

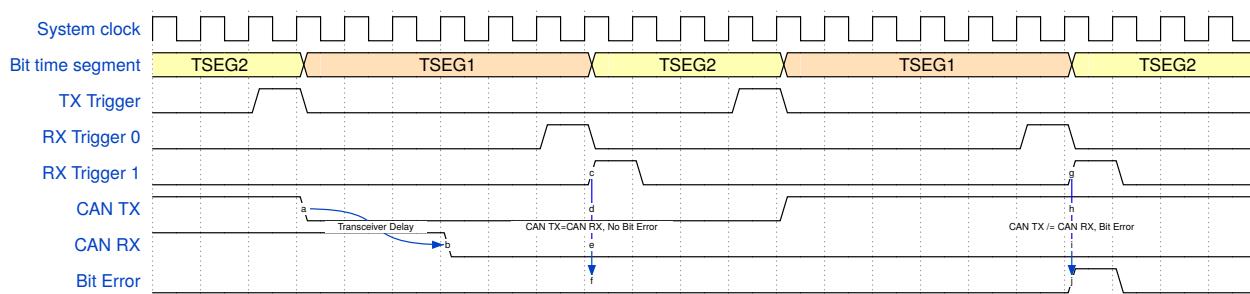

## 3.8 Pipeline architecture and triggers

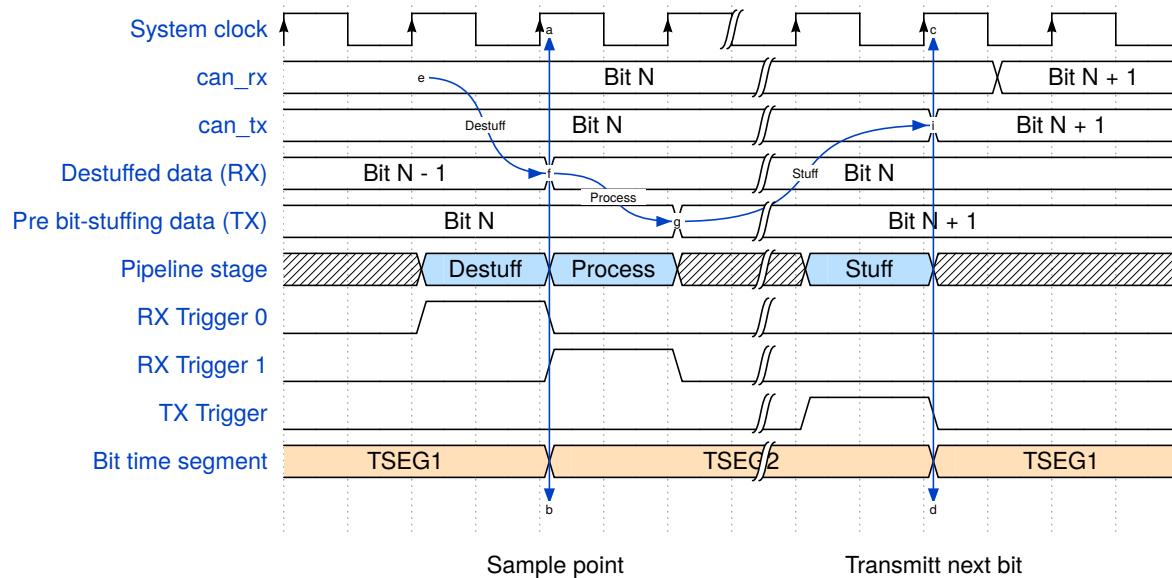

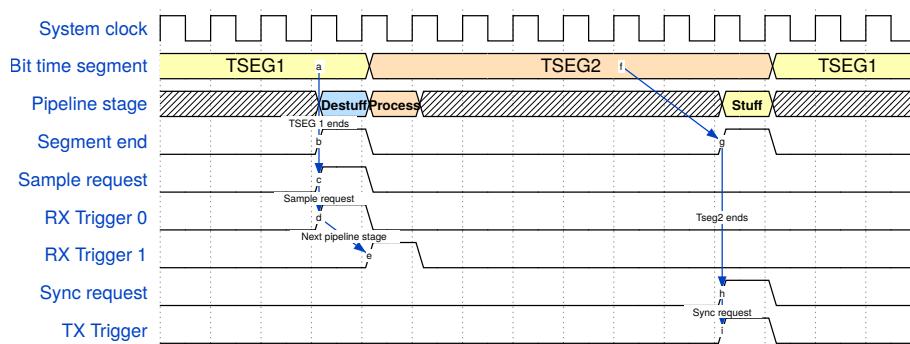

Processing of data on CAN bus in CTU CAN FD is pipelined into three stages which are described in Table 3.5. This architecture meets maximal **information processing time** when System clock is equal to **time quanta** (prescaler is 1). Since processing takes two clock periods **information processing time** of CTU CAN FD is 2. Due to this, **minimum time quanta** of CTU CAN FD is 1.

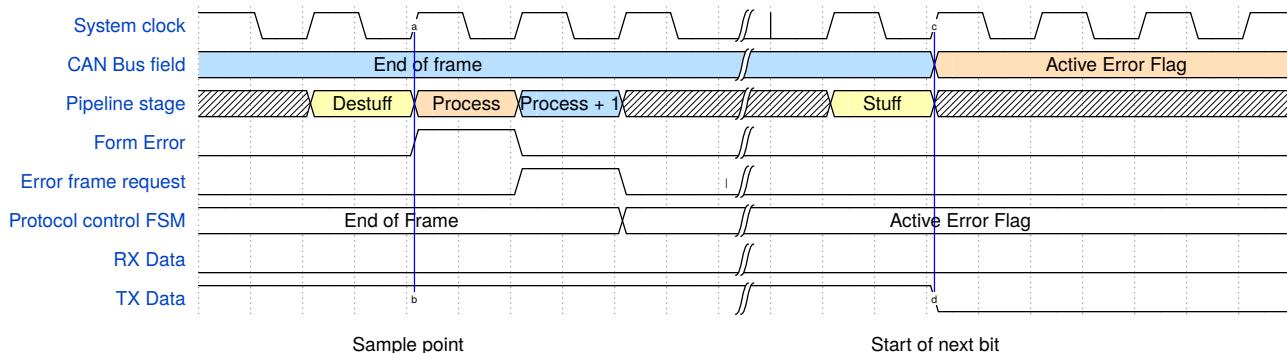

Each stage of pipeline processing is controlled by a trigger signal which is active for one clock cycle. Trigger signals are used to synchronise data transfer in exact moments to meet bit timing requirements on CAN Bus. Trigger signals are used as clock enable signals for DFF which processes data in according pipeline stage. If a trigger signal is inactive, processed data remain on DFF output and keep their previous value (data after bit destuffing (RX) and bit stuffing (TX)). An example of pipeline processing is shown in Figure 3.5. Note that Process pipeline stage always occurs one

clock cycle after Destuff pipeline stage. Between Process and Stuff pipeline stage there will be number of clock cycles where no data are processed. This gap corresponds to TSEG2 (see 4.7.1 for definition of TSEG2).

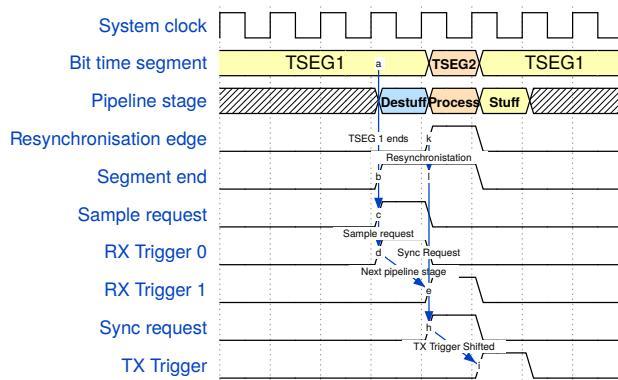

Figure 3.5: Datapath pipeline processing

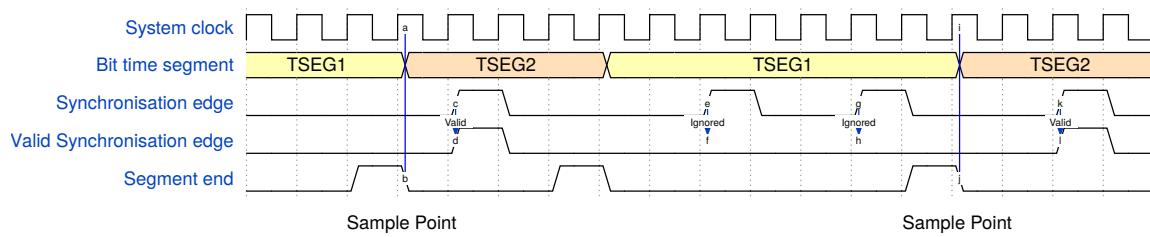

In case of **negative resynchronisation**, length of TSEG2 can be shortened to less than 2 clock cycles. In such case, following TX Trigger signal is throttled by one clock cycle and overall length of bit remains unaffected. Such situation is further described in 4.7.7. A high level algorithm for processing of data on CAN bus is described in Table 3.7.

Table 3.5: Pipeline stages

| Index | Pipeline stage | Trigger signal | Corresponding moment on CAN Bus    | Modules which process data in this pipeline stage | Description                                                                                                                                     |

|-------|----------------|----------------|------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Destuff        | RX Trigger (0) | Sample point                       | Bus Sampling, Bit Destuffing                      | Stuff Bits are removed from <b>can_rx</b> and destuffed data are provided to Protocol control.                                                  |

| 2     | Process        | RX Trigger (1) | One clock cycle after Sample point | Protocol Control                                  | Destuffed data are processed by Protocol control, value of following transmitted bit is determined and provided as TX data before bit stuffing. |

| 3     | Stuff          | TX Trigger     | Start of Bit time                  | Bit Stuffing                                      | Stuff bit is inserted to TX data before bit stuffing and propagated to <b>can_tx</b> .                                                          |

Table 3.7: Pipeline stages - algorithm

| Step | Step Description                                                                                                                                                                                                                                | Pipeline Stage        | Module           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|

| 1    | <b>can_rx</b> input is synchronised to System clock domain. Delay imposed by synchronisation is treated as wire delay and it is ignored.                                                                                                        | -                     |                  |

| 2    | Bus value is sampled to save information about previous sampled bus value for next edge detection. Synchronisation edges are detected on <b>can_rx</b> and propagated to Prescaler. <b>can_rx</b> value is propagated to Bit Destuffing module. | Destuff               | Bus Sampling     |

| 3    | <b>Bit de-stuffing</b> is performed in <b>Sample point</b> , and destuffed data are provided on output of Bit Destuffing module.                                                                                                                | Destuff               | Bit Destuffing   |

| 4    | CRC from RX bit value with stuff bits included ( <b>can_rx</b> ) is calculated.                                                                                                                                                                 | Destuff               | CAN CRC          |

| 5    | Destuffed data are sampled by Protocol control, RX shift register is shifted, TX shift register is preloaded by following bit to be transmitted, Protocol control FSM state is updated.                                                         | Process               | Protocol Control |

| 6    | CRC from destuffed data is calculated.                                                                                                                                                                                                          | Process               | CAN CRC          |

| 7    | <b>Stuff bits</b> are inserted to TX bit value on output of TX shift register by Bit Stuffing module. Value on output of Bit Stuffing module is propagated to <b>can_tx</b> output.                                                             | Stuff                 | Bit Stuffing     |

| 8    | TX shift register is shifted.                                                                                                                                                                                                                   | Stuff                 | Protocol Control |

| 9    | CRC from output of TX shift register (TX data before <b>bit stuffing</b> ) is calculated.                                                                                                                                                       | Stuff                 | CAN CRC          |

| 10   | CRC from TX data with <b>bit stuffing</b> is calculated. As this stage does not affect data transmitted on the bus in the actual bit, it is not considered as separate pipeline stage.                                                          | Stuff + 1 clock cycle | CAN CRC          |

## 3.9 CAN Frame metadata

Through this document, term “CAN frame metadata” is used to describe information shown in Table 3.8. In TXT buffers and RX buffer, metadata are stored in Frame Format word as is shown in Chapter 4 of [2].

## 3.10 CAN Frame format

CAN frame spans multiple 32-bit words in TXT buffers and within RX buffer RAMs (see 4.4 and 4.2). One TXT buffer always contains single frame. RX buffer contains multiple frames one after another in a RX buffer RAM. Format of CAN frame within these memories is the same with following exceptions:

- **ESI** bit in TXT buffer has no meaning while in RX buffer ESI has value of received **ESI** bit on CAN bus

- RWCNT field in TXT buffer has no meaning while in RX buffer it contains number of words that current frame takes in RX buffer without Frame Format word).

- FRAME\_TEST\_W word is available only in TXT buffer RAM, not in RX buffer RAM.

Meaning of memory words within CAN frame is described in Table 3.9. Meaning of individual bits can be found in Chapter 5 of [2].

Table 3.8: CAN frame metadata

| Name                        | Abbreviation | Possible values                         | Description                                                                                                                                                                                                         |

|-----------------------------|--------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Identifier type             | ID_TYPE      | BASE (0), EXTENDED (1)                  | Distinguishes frames with <b>base identifier</b> (BASE) only and frames with <b>identifier extension</b> (EXTENDED).                                                                                                |

| Frame type                  | FR_TYPE      | NORMAL_CAN (0), FD_CAN (1)              | Distinguishes CAN 2.0 frames and CAN FD frames.                                                                                                                                                                     |

| Remote Transmission Request | RTR          | NO_RTR_FRAME (0), RTR_FRAME (1)         | Distinguishes between <b>Data Frame</b> and <b>Remote frame</b> . When frame is CAN FD frame, RTR bit has no meaning.                                                                                               |

| Bit Rate Shift flag         | BRS          | BR_NO_SHIFT (0), BR_SHIFT (1)           | Distinguishes if <b>bit rate</b> will be shifted in CAN FD frame or not. This bit has no meaning in CAN 2.0 frames.                                                                                                 |

| Error State Indicator       | ESI          | ESI_ERR_ACTIVE (0), ESI_ERR_PASSIVE (1) | Value of received <b>ESI</b> bit. This bit has no meaning in CAN 2.0 frames. This bit has no meaning in TXT buffers. Value of transmitted <b>ESI</b> bit is always given by actual <b>Fault confinement state</b> . |

| Data length code            | DLC          | 0 - 15 as defined in [1]                | <b>Data length code</b> determines length of <b>data field</b> within CAN frame.                                                                                                                                    |

Table 3.9: CAN frame format - memory words

| Name of memory word | Name in register map (see [2]) | Description                                                                                                                        |

|---------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Frame Format        | FRAME_FORM_W                   | Contains CAN frame metadata and additional per-frame information.                                                                  |

| Identifier          | IDENTIFIER_W                   | Contains <b>base identifier</b> base and <b>identifier extension</b> .                                                             |

| Timestamp Low       | TIMESTAMP_L_W                  | Contains lower 32-bits of CAN frame Timestamp (in RX buffer as sampled during frame reception, in TXT buffer as inserted by user). |

| Timestamp High      | TIMESTAMP_U_W                  | Contains upper 32-bits of CAN frame Timestamp (in RX buffer as sampled during frame reception, in TXT buffer as inserted by user). |

| Data words          | DATA_X_Y_W                     | Contain CAN frame data payload transmitted/received during <b>data frame</b> field.                                                |

| Frame Test          | FRAME_TEST_W                   | Contains metadata for intentional corruption of transmitted CAN frames.                                                            |

### 3.11 Test mode

CTU CAN FD is in Test mode when MODE[TSTM] = '1'. Features of test mode are listed in Table 3.10.

Table 3.10: Test mode features

| Relevant register                        | Description                                                                                                                                                                                                                   |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTR_PRES                                 | CTR_PRES is writable and allows setting values of <b>transmitt error counter</b> , <b>receive error counter</b> , nominal error counter and data error counter.                                                               |

| EWL                                      | EWL register is read-write therefore Error warning limit is configurable by SW.                                                                                                                                               |

| ERP                                      | ERP register is read-write and Error passive threshold is configurable by SW. When either <b>transmitt error counter</b> or <b>receive error counter</b> reaches Error Passive threshold, unit becomes <b>error passive</b> . |

| TST_CONT, TST_DEST, TST_WDATA, TST_RDATA | Test registers are writable, therefore it is possible to directly read/write RX buffer RAM and TXT buffer RAMs. This feature is available only when <b>sup_test_registers</b> = true.                                         |

| FRAME_TEST_W                             | CAN FD uses bits in FRAME_TEST_W to intentionally corrupt transmitted CAN frames.                                                                                                                                             |

## 3.12 Integration vs. Reintegration

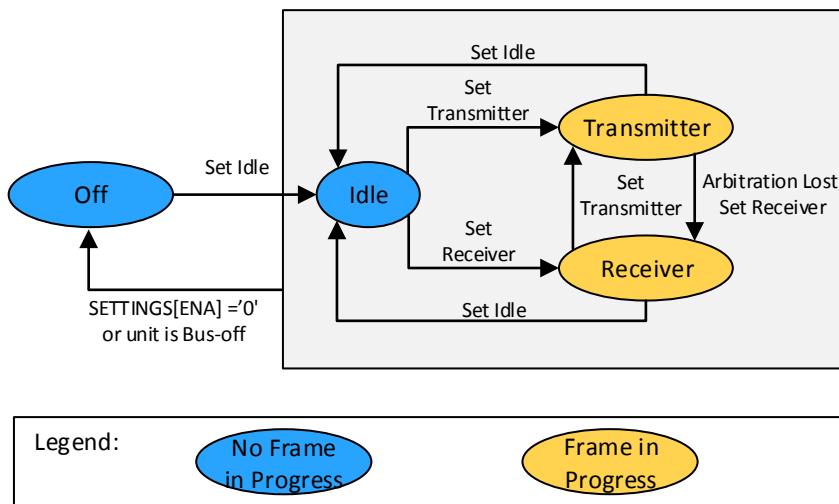

In this document term “Integration” means attempt to detect 11 consecutive **recessive** bits after logic 1 was written to SETTINGS[ENA] (CTU CAN FD was turned on). Term “Reintegration” means attempt to detect 129 occurrences of 11 consecutive recessive bits after node went **bus off** and logic 1 was written to COMMAND[ERCRST] (SW Requests to rejoin the bus).

# 4. Sub-blocks architecture

## 4.1 CAN Core

File: `can_core.vhd`

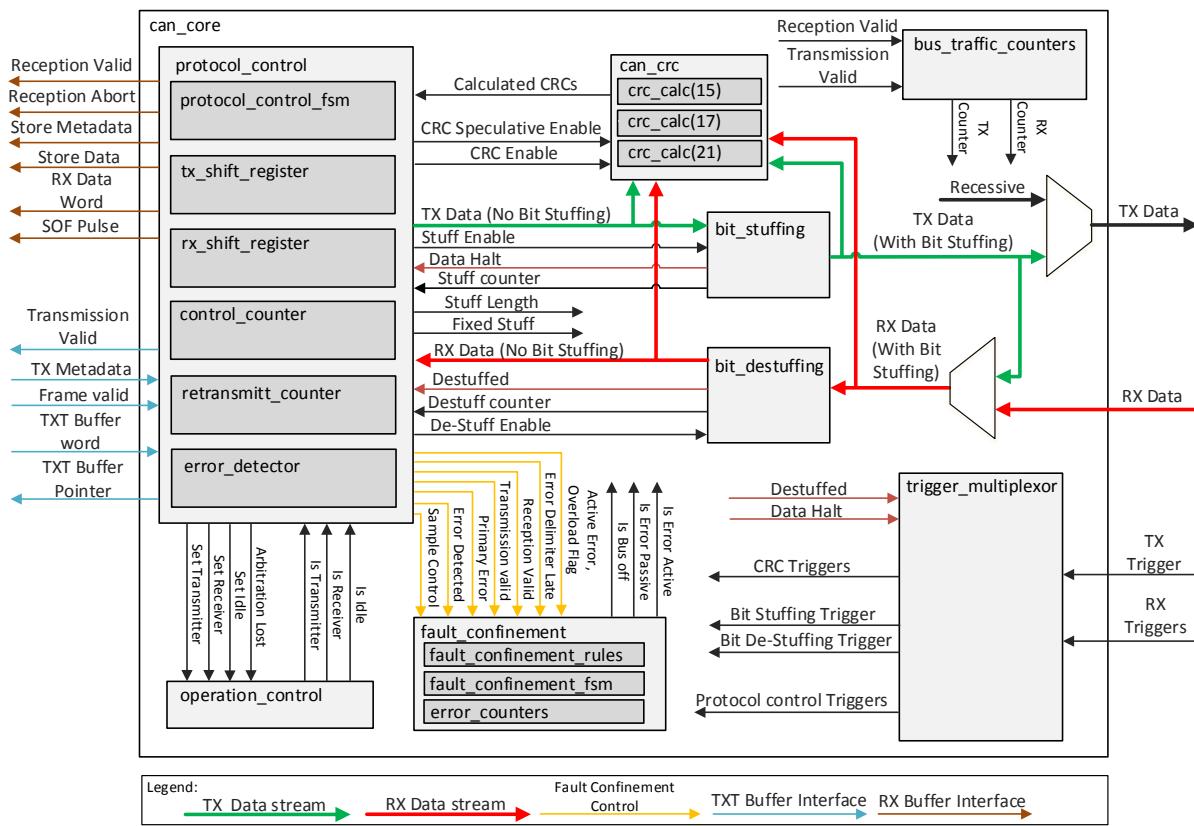

CAN core block diagram is shown in Figure 4.1. CAN core is structural entity that instantiates other modules and by itself it implements nearly no logic. An exception to this rule are two multiplexers as shown in Figure 4.1. Multiplexor on TX datapath (green color) multiplexes between transmitted data after **bit stuffing** or constant **recessive** value. Constant **recessive** value is sent to the bus in **bus monitoring mode**. Multiplexor on RX datapath (red color) multiplexes input data to Bit destuffing module. During normal operation, **can\_rx** input is used. When **secondary sample point** is used, data after **bit stuffing** are taken (transmitted data are looped back to make sure that Protocol control FSM receives proper value as real received value can be delayed by several bits). In **bus monitoring mode**, data after **bit stuffing** are logically ORed with **can\_rx** from input of CAN core (this corresponds to re-routing transmitted bit value internally as defined in 10.14 of [1]).

Figure 4.1: CAN Core - Block diagram

#### 4.1.1 Protocol control

File: protocol\_control.vhd

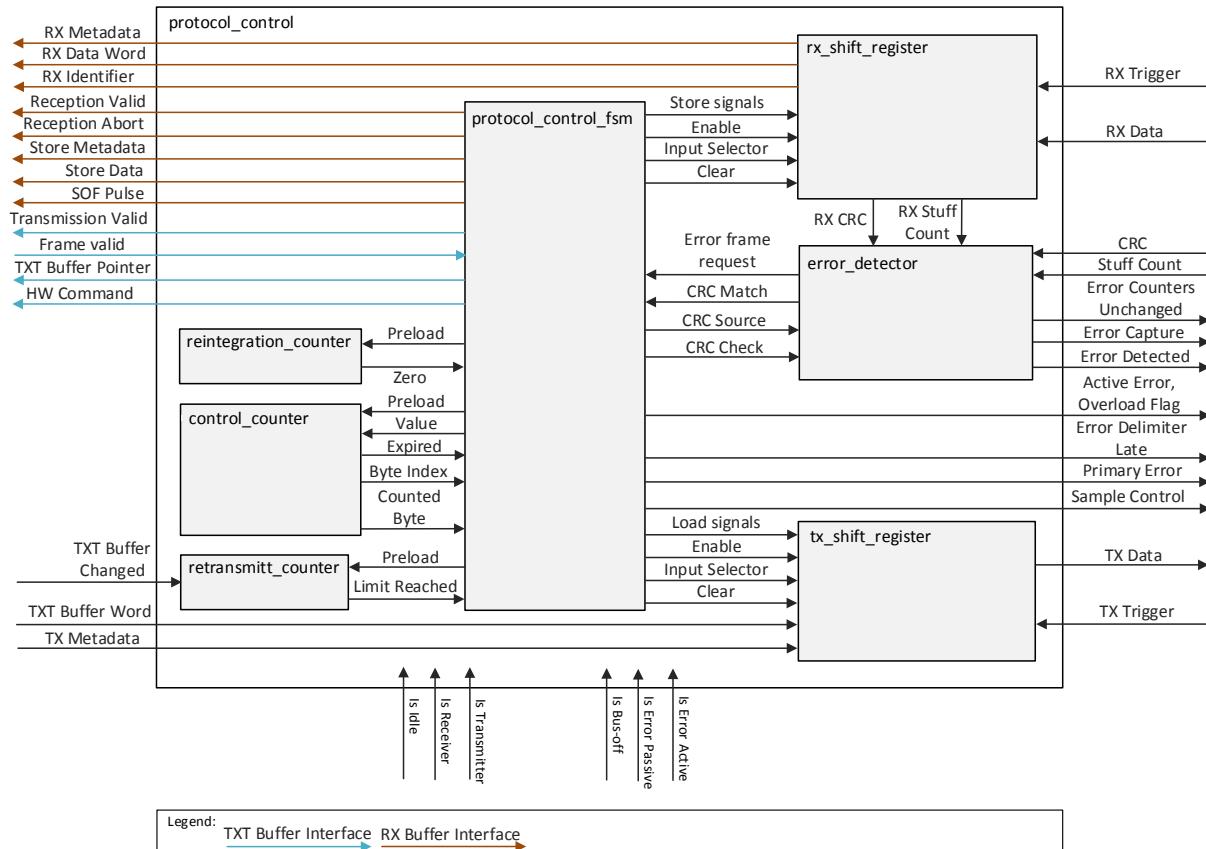

Protocol control diagram is shown in Figure 4.2. Protocol control is structural entity that only instantiates other modules and by itself it implements no logic.

Figure 4.2: Protocol control - Block diagram

## Protocol control FSM

File: protocol\_control\_fsm.vhd

Protocol control FSM implements following functionality:

- Transmits and receives CAN frames.

- Controls Control counter, Retransmitt Counter, Re-integration counter.

- Controls TX Shift Register.

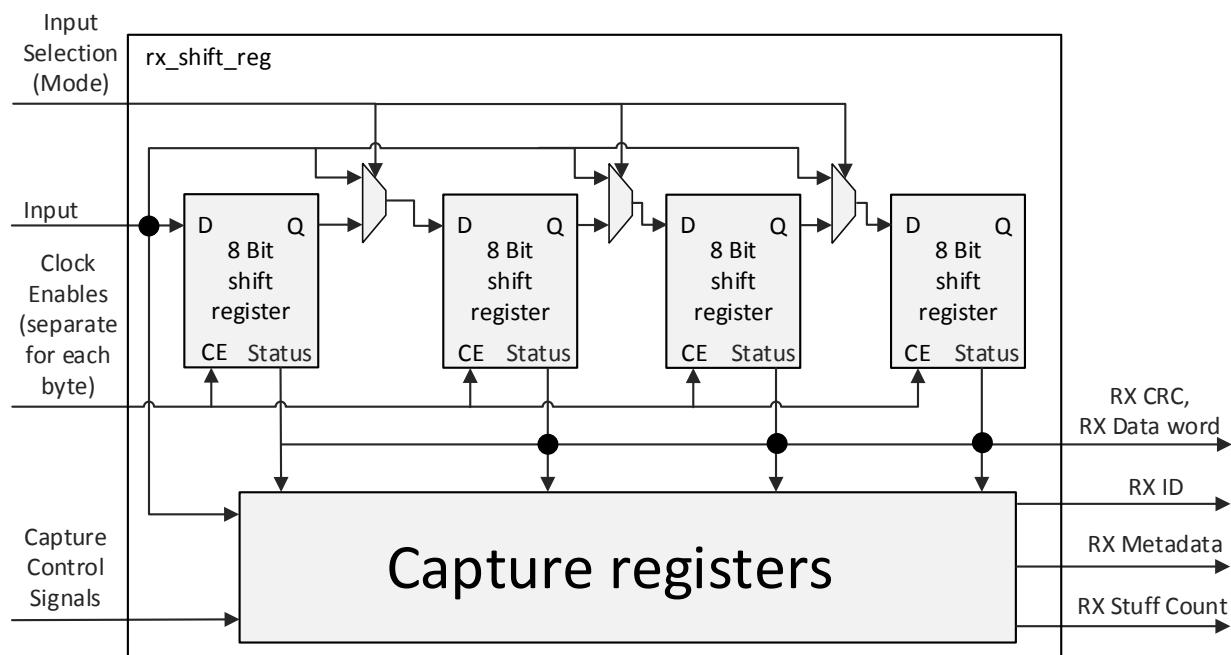

- Controls RX Shift Register. Storing values from RX Shift register to RX buffer.

- Reads transmitted frame from TXT buffer (addressing and reading data words from TXT buffer).

- Stores received frame to RX buffer.

- Controls measurement of **transmitter delay**.

- Controls TXT buffers and TX Arbitrator via HW Commands.

- Controls **synchronisation** (no **synchronisation**, **hard synchronisation**, **resynchronisation**)

- Controls **bit rate switching** (Nominal Sample, Data Sample, Secondary Sample).

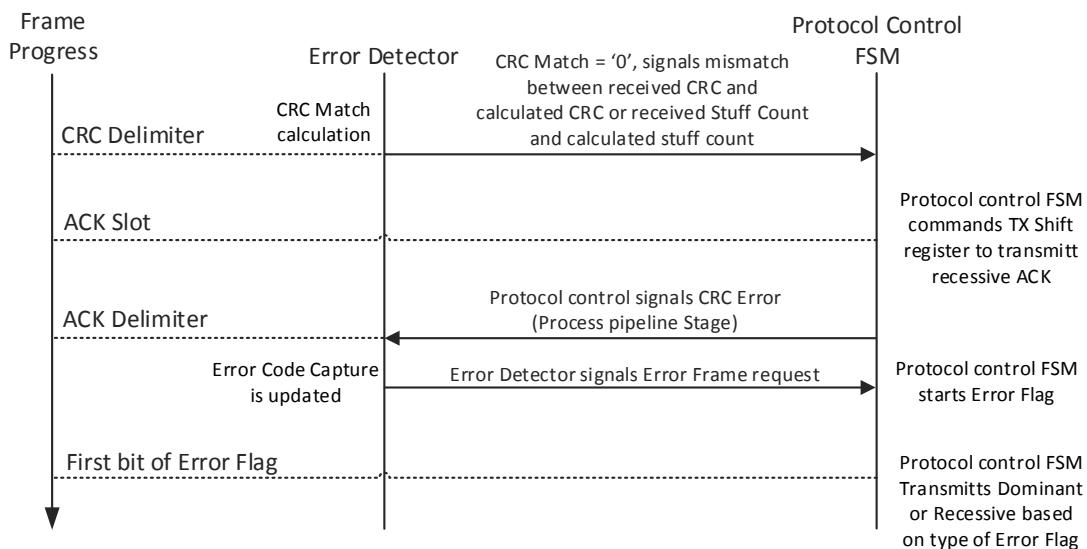

- Performs **form error** detection.

- Evaluates results of **CRC check**.

- Handles **arbitration**.

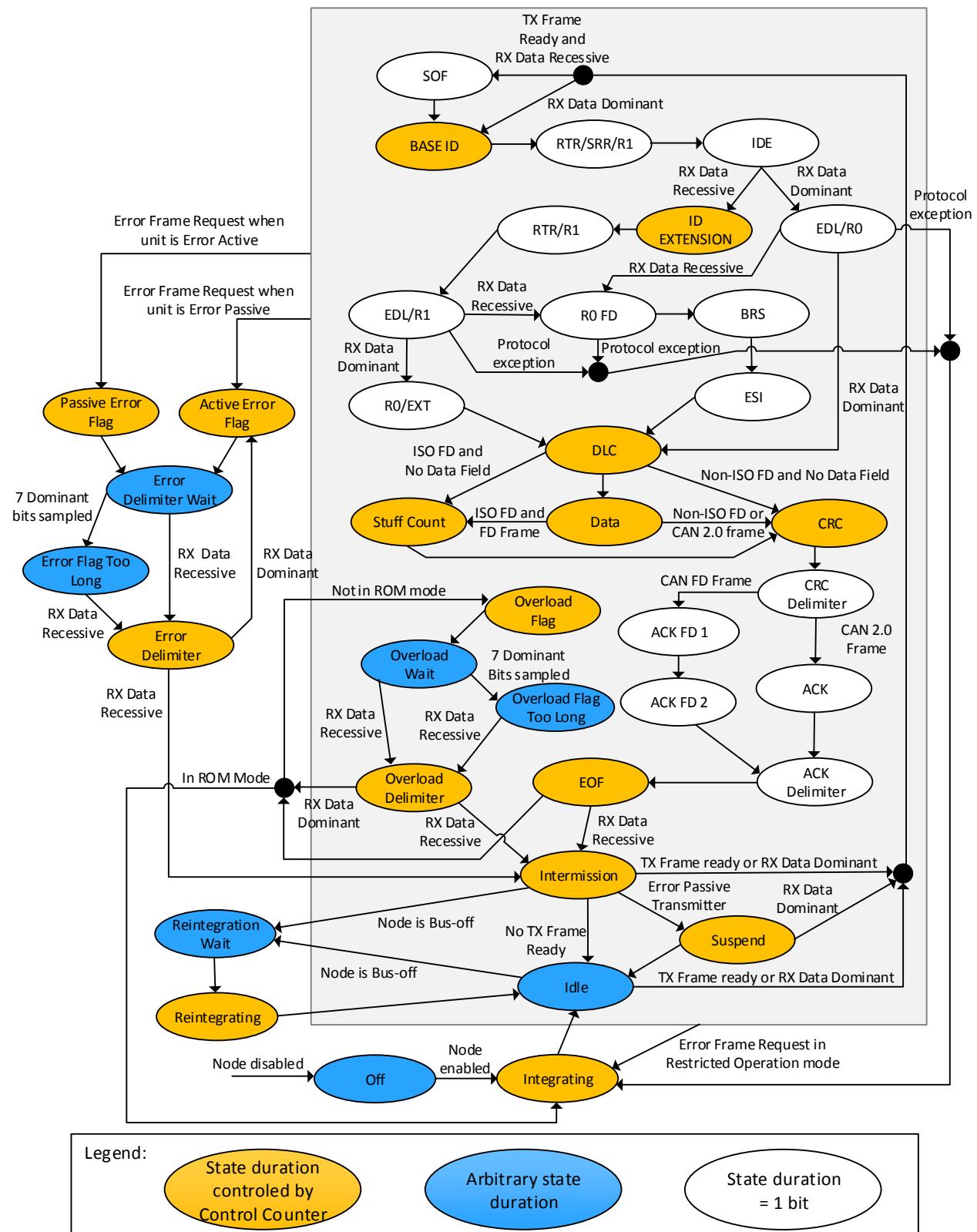

Protocol control FSM state transition diagram is shown in Figure 4.3. Rules for Protocol control FSM state transitions are described in Table 4.1. Protocol control FSM does not change its state in any other moment. The regular change of Protocol control FSM state corresponding to e.g. transition from **control field** to **data field** occurs one clock cycle after **sample point** (in Process pipeline stage).

Table 4.1: Protocol control state transition rules

| Condition of state transition | Pipeline stage when transition occurs | Description                                                                                                                                    |

|-------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Regular condition             | Process                               | Transition corresponds to regular change of CAN frame field (e.g. <b>stuff count</b> to <b>CRC</b> ).                                          |

| Error frame request           | One clock cycle after Process         | Transition corresponds to start of <b>active error flag</b> or <b>passive error flag</b> and can occur from any state of Protocol control FSM. |

Figure 4.3: Protocol control FSM

## Control counter

File: control\_counter.vhd

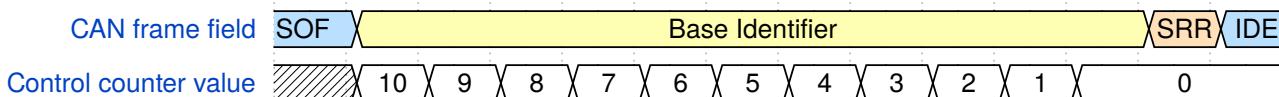

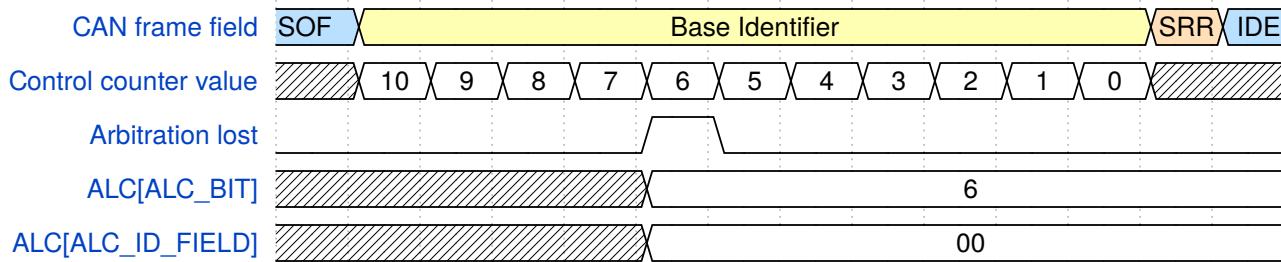

Control counter measures duration of CAN frame fields which last longer than 1 bit. These fields and according configuration of Control counter are shown in Table 4.2. Control counter counts towards zero. It is decremented by 1 in each bit of CAN frame field in Process pipeline stage. A current CAN frame field ends when Control counter is zero. Control counter is not counting during CAN frame fields which last only 1 bit (e.g. **IDE** bit), nor during fields which might last arbitrary number of bits (**bus idle**). An example of Control counter operation during **base identifier** in CAN frame is shown in Figure 4.4.

Table 4.2: Control counter

| CAN Frame field                     | Control counter preload value                        |

|-------------------------------------|------------------------------------------------------|

| Base identifier                     | 10                                                   |

| Identifier extension                | 17                                                   |

| Data length code                    | 3                                                    |

| Data                                | Depends on transmitted / received data field length. |

| CRC                                 | 14, 16, 20 - depends on length of CRC sequence       |

| Stuff count (+ Stuff parity)        | 3                                                    |

| End of Frame                        | 7                                                    |

| Interframe space                    | 2                                                    |

| Suspend transmission                | 7                                                    |

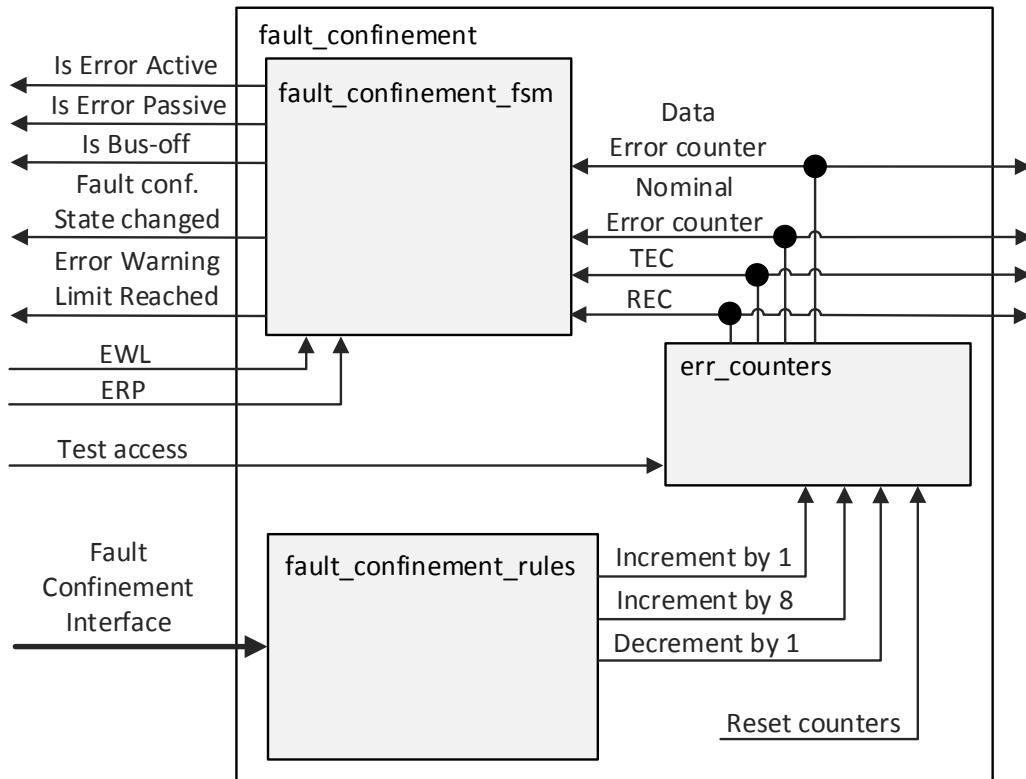

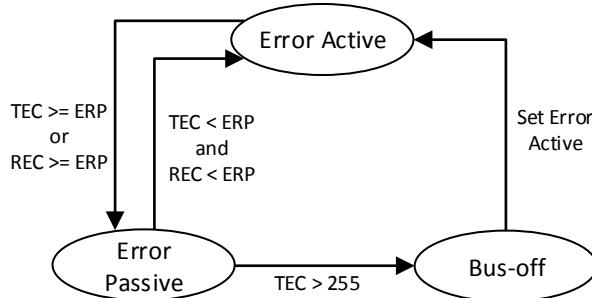

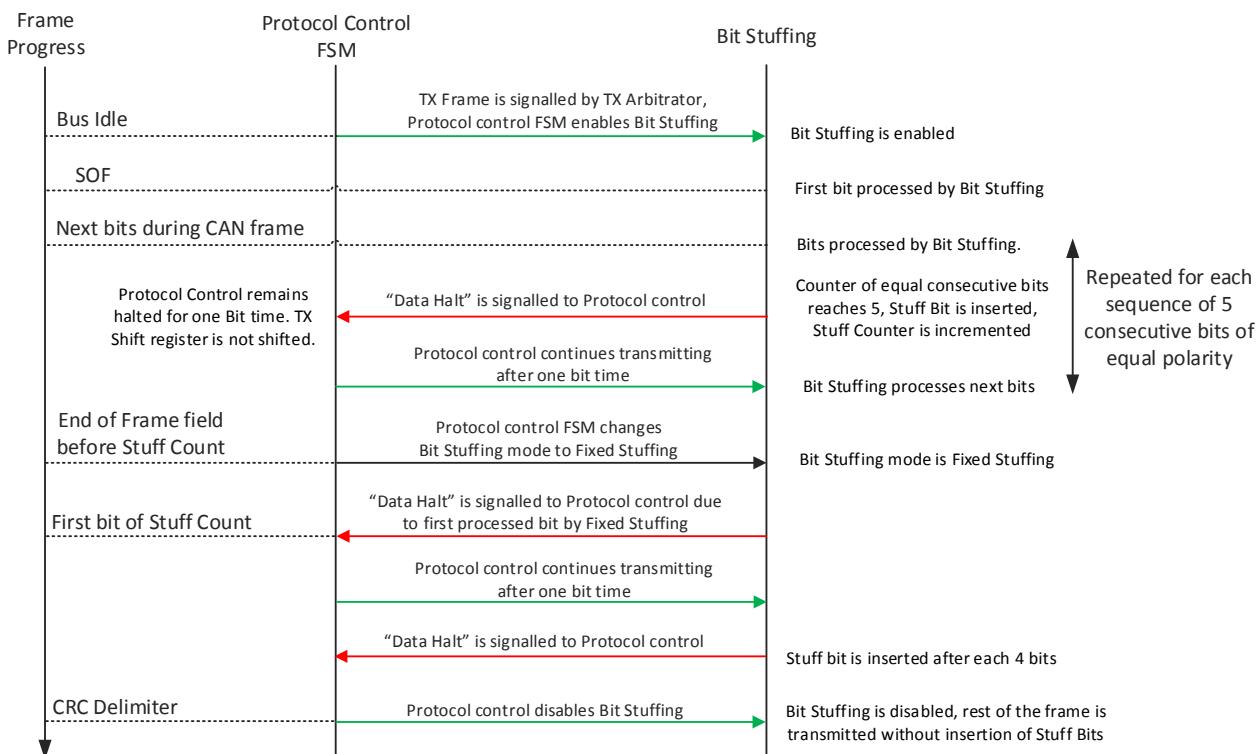

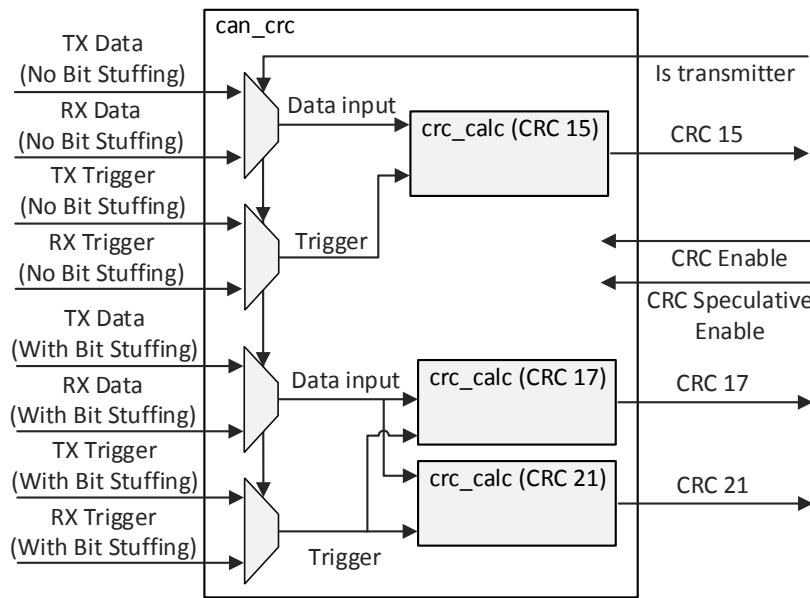

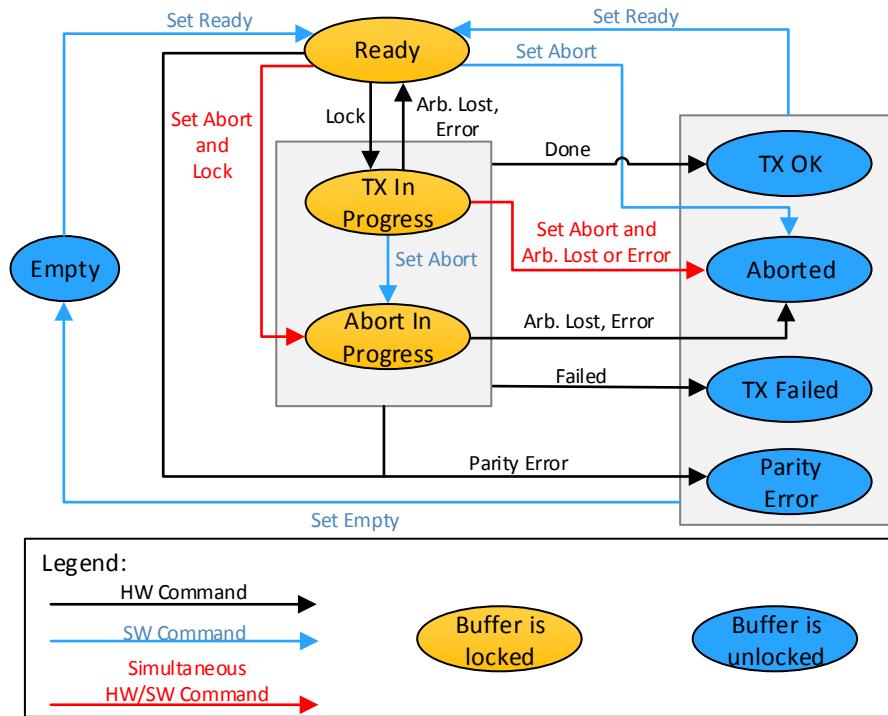

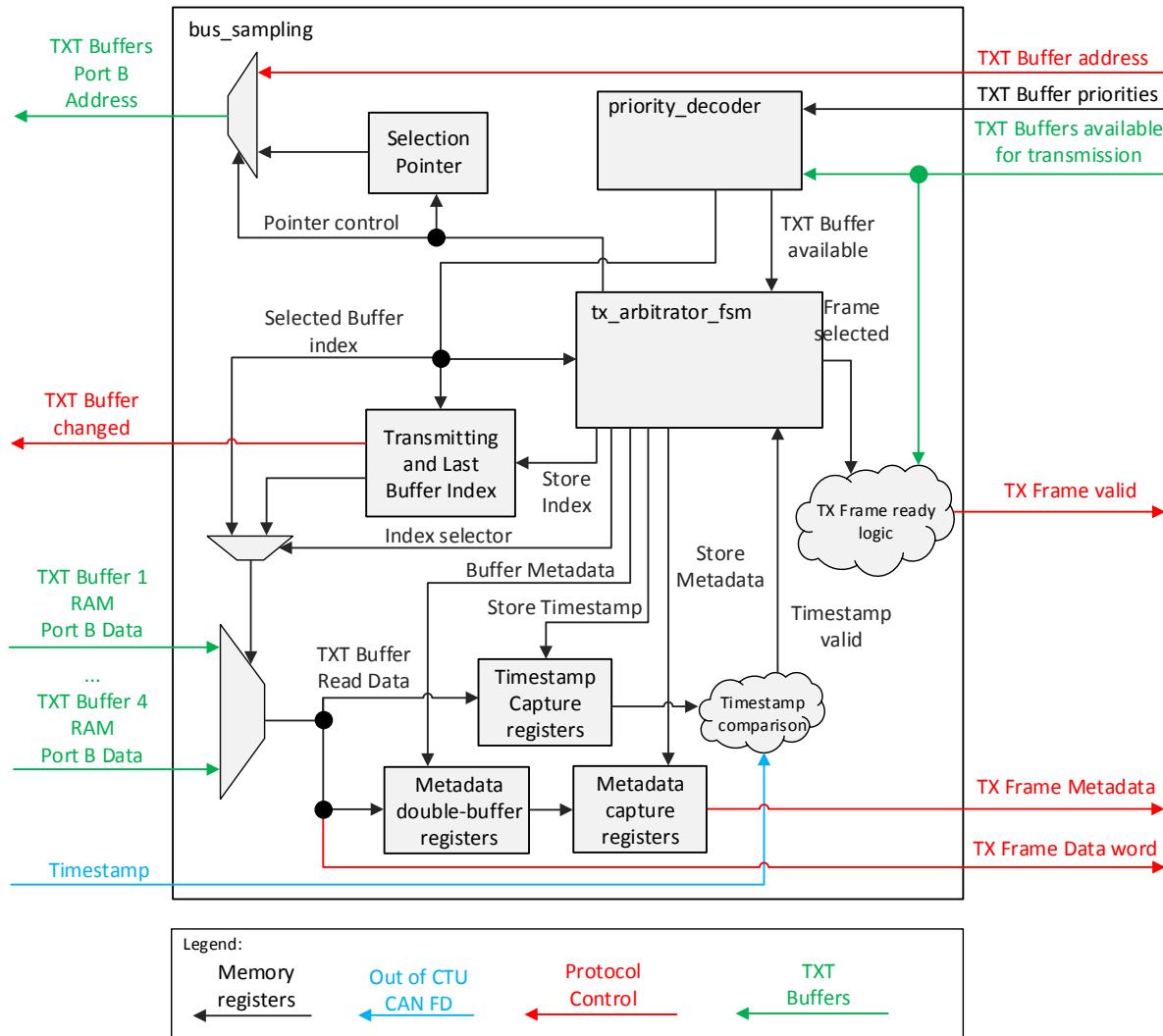

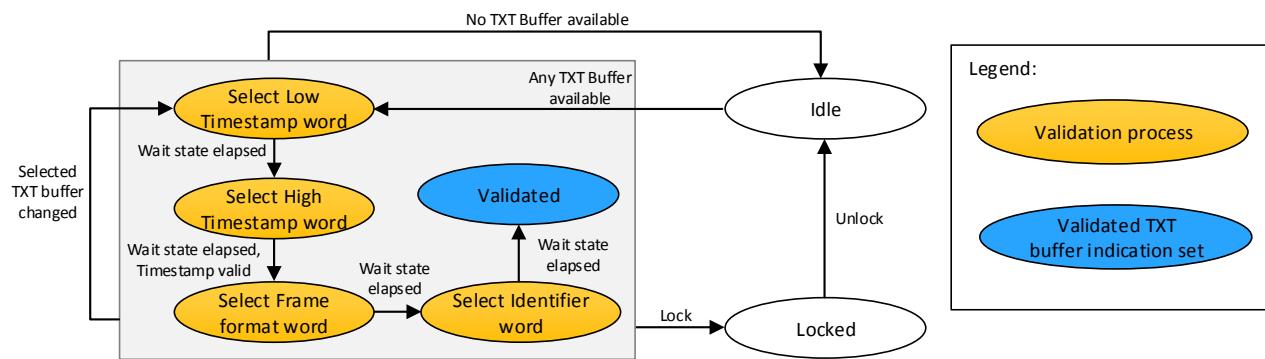

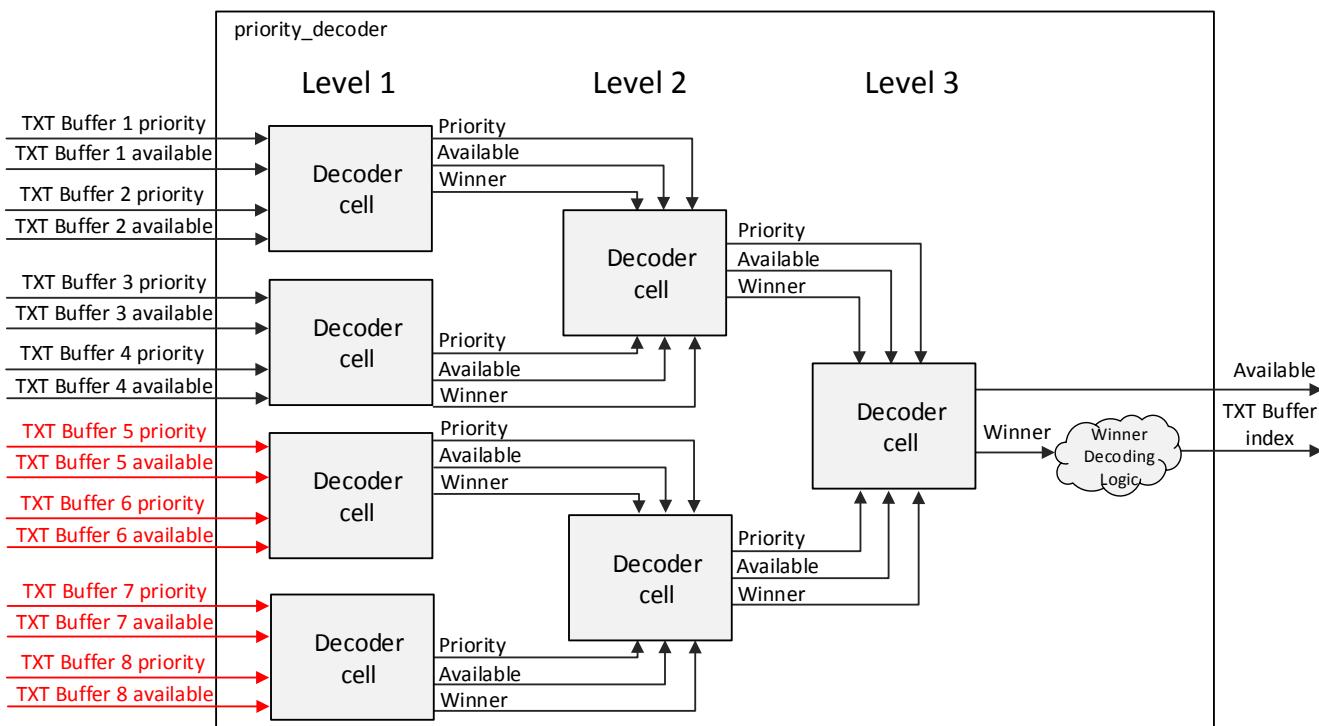

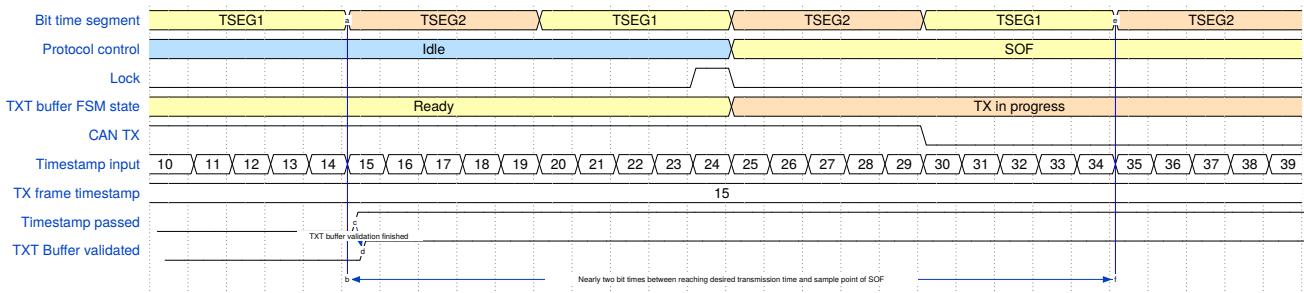

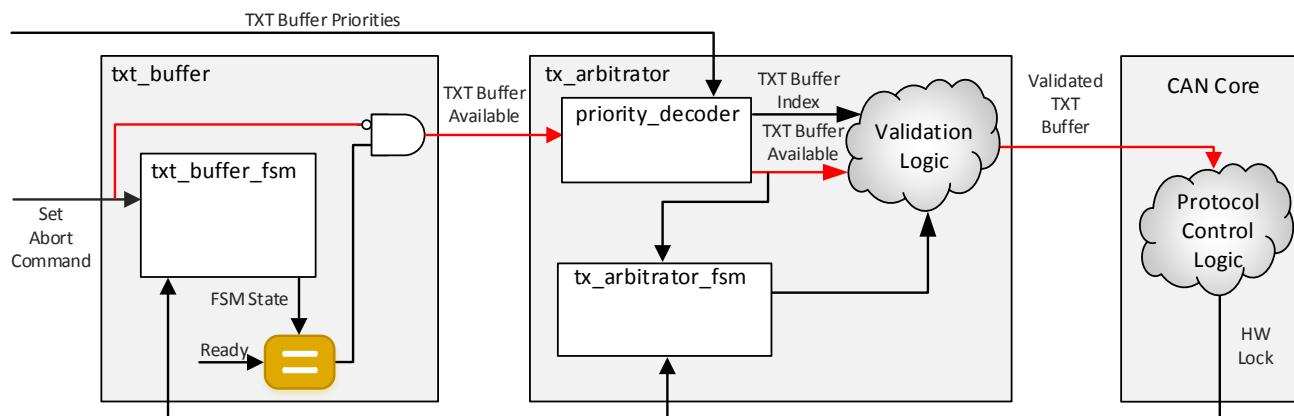

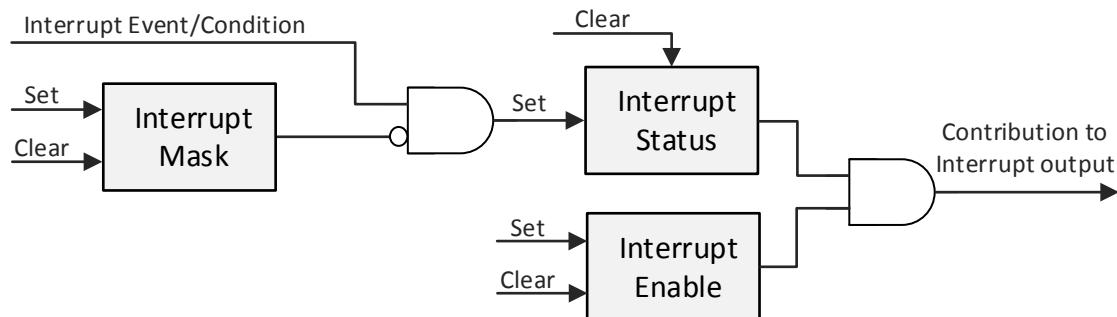

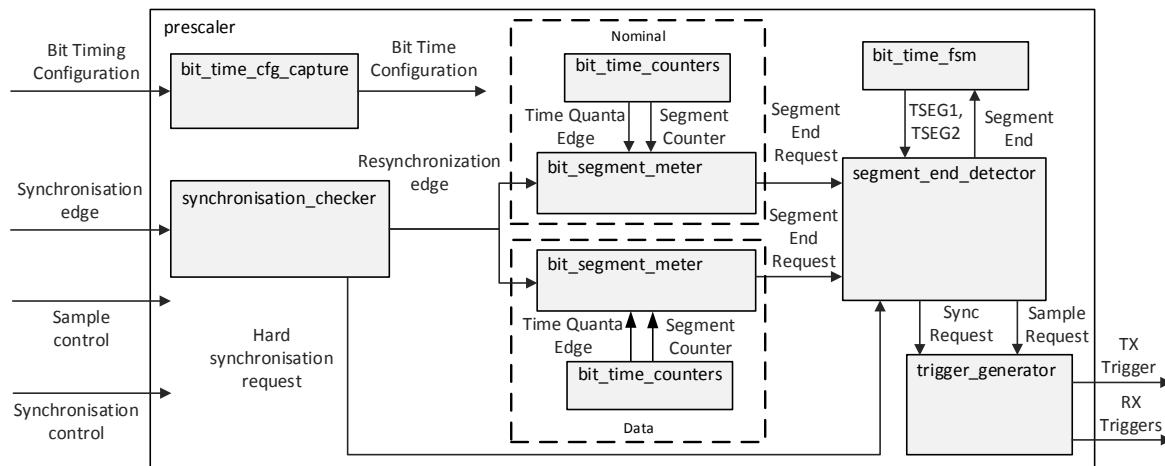

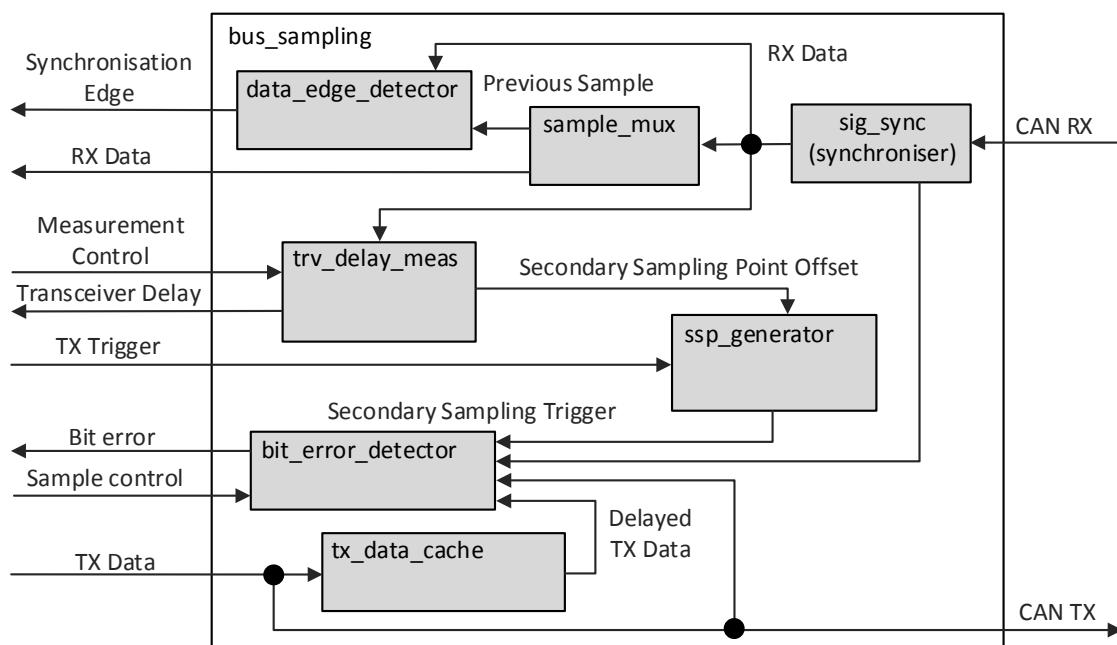

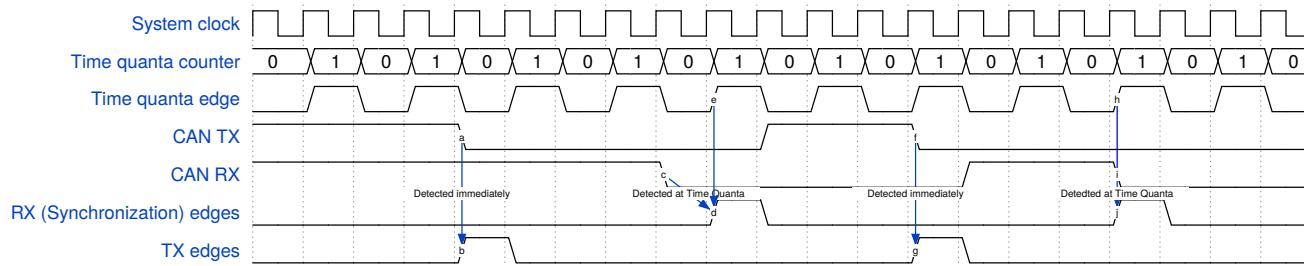

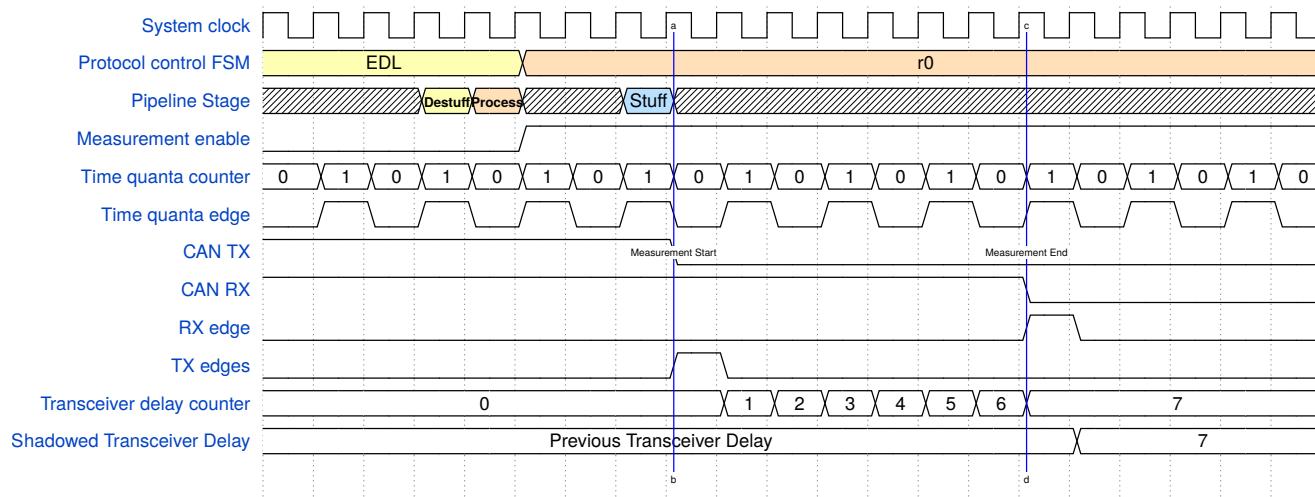

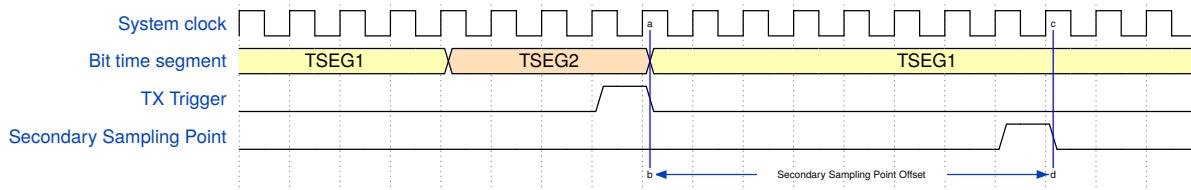

| Integration                         | 10                                                   |